# CprE / ComS 583 Reconfigurable Computing

Prof. Joseph Zambreno Department of Electrical and Computer Engineering Iowa State University

Lecture #25 - High-Level Compilation

| Sunday              | Monday | Tuesday                                        | Wednesday                | Thursday                             | Friday | Saturday                               |

|---------------------|--------|------------------------------------------------|--------------------------|--------------------------------------|--------|----------------------------------------|

| 25                  | 26     | 27                                             | 28                       | 29                                   | 30     | 1                                      |

|                     |        | Lect-25                                        |                          | Lect-26                              |        |                                        |

| 2<br>Dead<br>Week   | 3      | 4<br>Project<br>Seminars<br>(EDE) <sup>1</sup> | 5                        | 6<br>Project<br>Seminars<br>(Others) | 7      | 8                                      |

| 9<br>Finals<br>Week | 10     | 11                                             | 12                       | 13                                   | 14     | 15<br>Project<br>Write-ups<br>Deadline |

| 16                  | 17     | 18<br>Electronic<br>Grades<br>Due              | December / November 2007 |                                      |        |                                        |

#### Project Deliverables

- · Final presentation [15-25 min]

- Aim for 80-100% project completeness

- · Outline it as an extension of your report:

- Motivation and related work

- Analysis and approach taken

- Experimental results and summary of findings

- Conclusions / next steps

- Consider details that will be interesting / relevant for the expected audience

- · Final report [8-12 pages]

- More thorough analysis of related work

- Minimal focus on project goals and organization

- · Implementation details and results

- See proceedings of FCCM/FPGA/FPL for inspiration

November 27, 200

CprE 583 – Reconfigurable Computing

# Recap – Reconfigurable Coprocessing

- Processors efficient at sequential codes, regular arithmetic operations

- FPGA efficient at fine-grained parallelism, unusual bit-level operations

- Tight-coupling important: allows sharing of data/control

- Efficiency is an issue:

- Context-switches

- · Memory coherency

- Synchronization

November 27, 2007

prE 583 – Reconfigurable Computing

Lect-25.4

# ••• Instruction Augmentation

- Processor can only describe a small number of basic computations in a cycle

- I bits -> 2 operations

- Many operations could be performed on 2 W-bit words

- ALU implementations restrict execution of some simple operations

e. g. bit reversal

November 27, 200

CprE 583 – Reconfigurable Computing

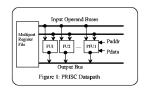

# Recap – PRISC [RazSmi94A]

- Architecture:

- couple into register file as "superscalar" functional unit

- flow-through array (no state)

November 27, 20

orE 583 - Reconfigurable Computing

CprE 583 - Reconfig

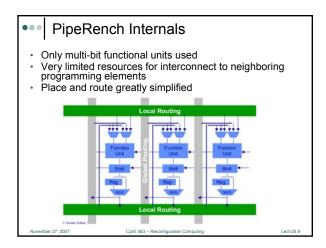

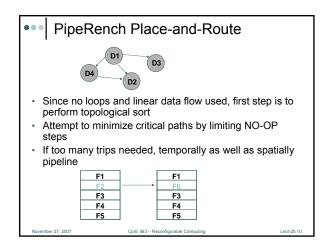

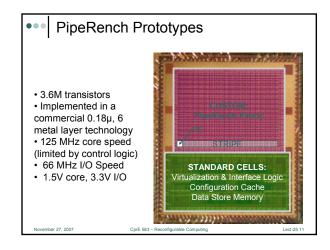

### ••• PipeRench Architecture

- · Many application are primarily linear

- Audio processing

- · Modified video processing

- Filtering

- Consider a "striped" architecture which can be very heavily pipelined

- Each stripe contains LUTs and flip flops

- · Datapath is bit-sliced

- · Similar to Garp/Chimaera but standalone

- Compiler initially converts dataflow application into a series of stripes

- Run-time dynamic reconfiguration of stripes if application is too big to fit in available hardware

ovember 27, 2007

CprE 583 – Reconfigurable Computing

Loct 25 9

# Parallel Computation

What would it take to let the processor and FPGA run in parallel?

#### Modern Processors

#### Deal with:

- · Variable data delays

- · Dependencies with data

- Multiple heterogeneous functional units

#### Via:

- Register scoreboarding

- Runtime data flow (Tomasulo)

lovember 27, 2007

CprE 583 – Reconfigurable Computing

ect-25.12

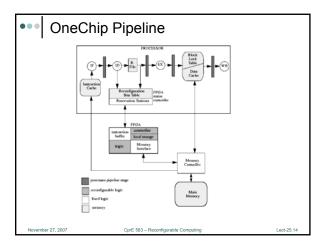

### ••• OneChip

- Want array to have direct memory

operations

- Want to fit into programming model/ISA

- Without forcing exclusive processor/FPGA operation

- Allowing decoupled processor/array execution

- Key Idea:

- FPGA operates on memory→memory regions

- · Make regions explicit to processor issue

- Scoreboard memory blocks

November 27, 2007

CprE 583 - Reconfigurable Computing

Lect-25.13

#### ••• OneChip Instructions

- · Basic Operation is:

- FPGA MEM[Rsource]→MEM[Rdst]

- block sizes powers of 2

- Supports 14 "loaded" functions

- DPGA/contexts so 4 can be cached

- · Fits well into soft-core processor model

November 27, 200

CprE 583 – Reconfigurable Computing

ect-25.15

### ••• OneChip (cont.)

- Basic op is: FPGA MEM→MEM

- · No state between these ops

- · Coherence is that ops appear sequential

- Could have multiple/parallel FPGA compute units

- Scoreboard with processor and each other

- Single source operations?

- · Can't chain FPGA operations?

November 27, 20

orE 583 – Reconfigurable Computing

Lect-25.1

# ••• OneChip Extensions

- FPGA operates on certain memory regions only

- · Makes regions explicit to processor issue

- · Scoreboard memory blocks

Indicates usage of data pages like virtual memory system!

November 27, 2007

CprE 583 – Reconfigurable Computing

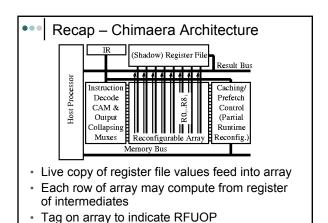

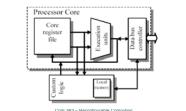

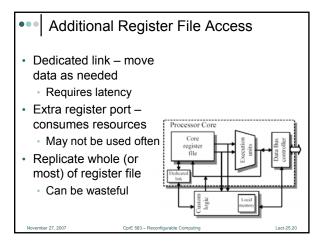

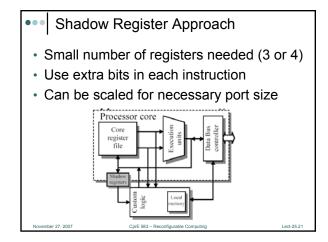

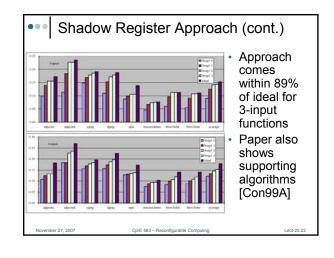

# Shadow Registers

- Reconfigurable functional units require tight integration with register file

- Many reconfigurable operations require more than two operands at a time

77 CprE 583 – Recontigurable Computing Lect-25

# Multi-Operand Operations What's the best speedup that could be achieved? Provides upper bound Assumes all operands available when needed November 27, 2007 Cpr: S03 - Reconfigurable Computing Lect 25, 19

# ••• Summary

- Many different models for co-processor implementation

- Functional unit

- · Stand-alone co-processor

- Programming models for these systems is a key

- Recent compiler advancements open the door for future development

- Need tie in with applications

November 27, 2007

CprE 583 – Reconfigurable Computing

ect-25.23

# Outline

- Recap

- · High-Level FPGA Compilation

- Issues

- · Handel-C

- DeepC

- · Bit-width Analysis

November 27, 2007

rE 583 – Reconfigurable Computing

,

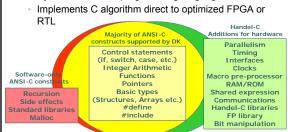

#### ••• Overview

- High-level language to FPGA an important research area

- Many challenges

- Commercial and academic projects

- Celoxica

- DeepC

- Stream-C

- · Efficiency still an issue

- Most designers prefer to get better performance and reduced cost

- Includes incremental compile and hardware/software codesign

louombor 27, 2007

CprE 583 - Reconfigurable Computing

Lect-25.25

#### ••• Issues

- Languages

- Standard FPGA tools operate on Verilog/VHDL

- · Programmers want to write in C

- · Compilation Time

- Traditional FPGA synthesis often takes hours/days

- Need compilation time closer to compiling for conventional computers

- Programmable-Reconfigurable Processors

- Compiler needs to divide computation between programmable and reconfigurable resources

- Non-uniform target architecture

- Much more variance between reconfigurable architectures than current programmable ones

November 27, 2007

CprE 583 - Reconfigurable Computing

Loot 25 26

#### ••• Why Compiling C is Hard

- General language

- · Not designed for describing hardware

- · Features that make analysis hard

- Pointers

- Subroutines

- Linear code

- · C has no direct concept of time

- C (and most procedural languages) are inherently sequential

- Most people think sequentially

- · Opportunities primarily lie in parallel data

November 27, 20

CprE 583 – Reconfigurable Computing

Lect-25.27

#### Notable Platforms

- · Celoxica Handel-C

- · Commercial product targeted at FPGA community

- · Requires designer to isolate parallelism

- · Straightforward vision of scheduling

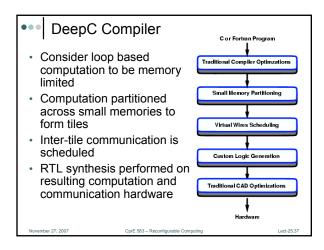

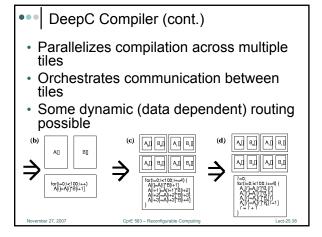

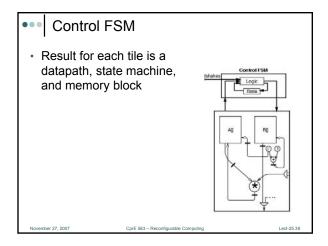

- DeepC

- · Completely automated no special actions by designer

- Ideal for data parallel operation

- Fits well with scalable FPGA model

- Stream-C

- Computation model assumes communicating processes

- Stream based communication

- Designer isolates streams for high bandwidth

November 27, 2007

CprE 583 – Reconfigurable Computing

Lect-25.28

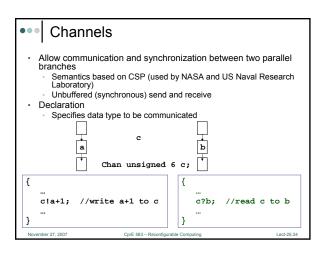

## Celoxica Handel-C

- Handel-C adds constructs to ANSI-C to enable hardware implementation

- Synthesizable HW programming language based on C

#### Fundamentals

- Language extensions for hardware implementation as part of a system level design methodology

- Software libraries needed for verification

- Extensions enable optimization of timing and area performance

- Systems described in ANSI-C can be implemented in software and hardware using language extensions defined in Handel-C to describe hardware

- Extensions focused towards areas of parallelism and communication

lovember 27, 200

CprE 583 – Reconfigurable Computing

Lect-25.30

# Variables Handel-C has one basic type - integer May be signed or unsigned Can be any width, not limited to 8, 16, 32 etc. Variables are mapped to hardware registers void main(void) { unsigned 6 a; a=45; } a = 1 0 1 1 0 1 = 0x2d MsB LSB November 27, 2007

```

Timing Model

Assignments and delay statements take 1 clock cycle

Combinatorial Expressions computed between clock edges

Most complex expression determines clock period

Example: takes 1+n cycles (n is number of iterations)

index = 0;  // 1 Cycle

while (index < length) {

if(table[index] = key)

found = index;  // 1 Cycle</li>

else

index = index+1;  // 1 Cycle

}

}

```

```

Parallelism

· Handel-C blocks are by default sequential

par{...} executes statements in parallel

· Par block completes when all statements complete

Time for block is time for longest statement

Can nest sequential blocks in par blocks

· Parallel version takes 1 clock cycle

Allows trade-off between hardware size and performance

Parallel Block

// 1 Clock Cycle

Parallel code

par{

par(i=0;i<10;i++)

a=1:

b=2:

array[i]=0;

c=3;

```

```

• A signal behaves like a wire - takes the value assigned to it but only for that clock cycle

• The value can be read back during the same clock cycle

• The signal can also be given a default value

// Breaking up complex expressions

int 15 a, b;

signal <int> sig1;

static signal <int> sig2=0;

a = 7;

par

{

sig1 = (a+34)*17;

sig2 = (a<<2)+2;

b = sig1 + sig2;

}

November 27, 2007 Cptf: 583 - Reconfigurable Computing

Lect 2535

```

```

Functions provide a means of sharing hardware for expressions

By default, compiler generates separate hardware for each expression

Hardware is idle when control flow is elsewhere in the program

Hardware function body is shared among call sites

int mult_add(int z,c1,c2){

xe x*a + b;

ye y*c + d;

memult_add(x,a,b);

ye mult_add(y,c,d);

}

```

Sharing Hardware for Expressions

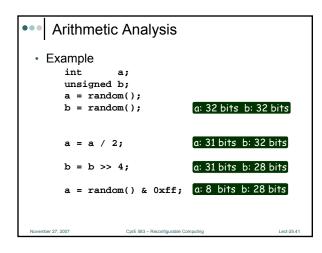

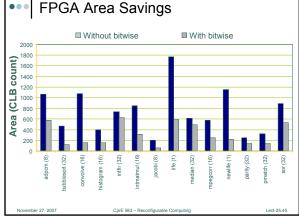

Bit-width Analysis

Higher Language Abstraction

Reconfigurable fabrics benefit from specialization

One opportunity is bitwidth optimization

During C to FPGA conversion consider operand widths

Requires checking data dependencies

Must take worst case into account

Opportunity for significant gains for Booleans and loop indices

Focus here is on specialization

```

Loop Induction Variable Bounding

Applicable to for loop induction variables.

Example

int i;

i: 32 bits

for (i = 0; i < 6; i++) {

<ul>

i: 3 bits

i: 3 bits

```

# Clamping Optimization Multimedia codes often simulate saturating instructions Example int valpred if (valpred > 32767) valpred = 32767 else if (valpred < -32768) valpred = -32768 valpred: 16 bits</li>

Can easily find conservative range of <0,510>

ber 27,2007 CprE 583 – Reconfigurable Computing

# ••• Summary

- High-level is still not well understood for reconfigurable computing

- Difficult issue is parallel specification and verification

- Designers efficiency in RTL specification is quite high. Do we really need better high-level compilation?

iber 27, 2007 CprE 583 – Reconfigurable Cor

8