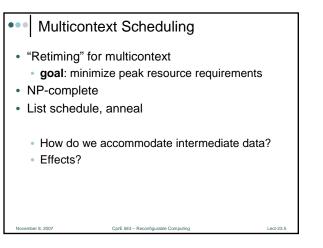

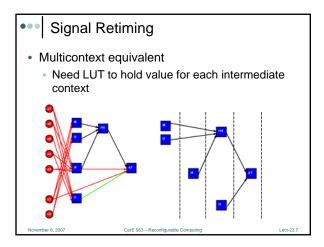

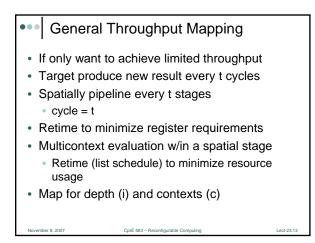

How will it show up in multicontext?

CprE 583 - Re

November 8, 2007

| • 23    | nchmarl<br>MCNC cii<br>.rea mapp | rcuits      | SIS ai  | nd Chortle  | )           |

|---------|----------------------------------|-------------|---------|-------------|-------------|

| Circuit | Mapped LUTs                      | Path Length | Circuit | Mapped LUTs | Path Length |

| 5xp1    | 46                               | 10          | des     | 1267        | 13          |

| 9sym    | 123                              | 7           | e64     | 230         | 9           |

| 9symml  | 108                              | 8           | f51m    | 45          | 17          |

| C499    | 85                               | 10          | misex1  | 20          | 6           |

| C880    | 176                              | 21          | misex2  | 38          | 8           |

| alu2    | 169                              | 19          | rd73    | 105         | 10          |

| apex6   | 248                              | 9           | rd84    | 150         | 9           |

| apex7   | 77                               | 7           | rot     | 293         | 16          |

| b9      | 46                               | 7           | sao2    | 73          | 9           |

| clip    | 121                              | 9           | vg2     | 60          | 9           |

| cordic  | 367                              | 13          | z4ml    | 8           | 7           |

| count   | 46                               | 16          |         |             |             |

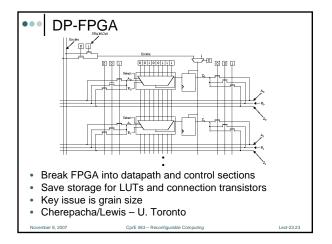

## ••• DP-FPGA Technology Mapping

- Ideal case would be if all datapath divisible by 4, no "irregularities"

- Area improvement includes logic values only

- Shift logic included

| Clash   |          | rando Mel | \$ | Constants<br>area: Marai | Anna (40)<br>Anna (40) |

|---------|----------|-----------|----|--------------------------|------------------------|

| ļ       | 927      | ř.        | л  |                          | Ę                      |

| and a   | <b>ന</b> | LØN       | 19 | 146                      | 11                     |

| energie | 348      | 161       | 1  | 2005                     | 24                     |

| Čier:   | 24       |           | 8  | 56                       | บ                      |

| Şulik:  | 36       |           | 19 | 348                      | 24                     |

| ladaat. | up 🗤     | 9         | 18 |                          | 24                     |

|         | #        | u         | 49 |                          | L.                     |

| -       | 710      |           | 18 | 39                       | 24                     |

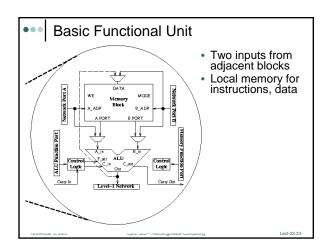

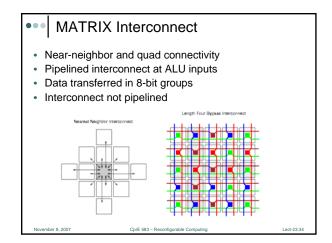

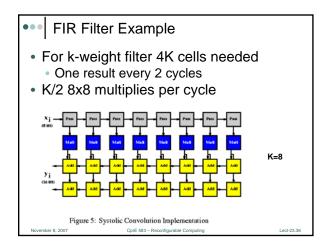

## ••• MATRIX

- Dehon and Mirsky -> MIT

- 2-dimensional array of ALUs

- Each Basic Functional Unit contains "processor" (ALU + SRAM)

- Ideal for systolic and VLIW computation

- 8-bit computation

per 8, 2007

• Forerunner of SiliconSpice product

CprE 583 - Reconfig

Lect-23.3

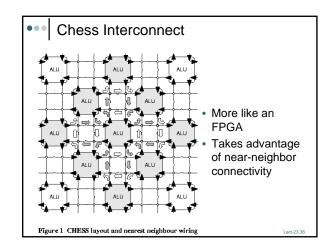

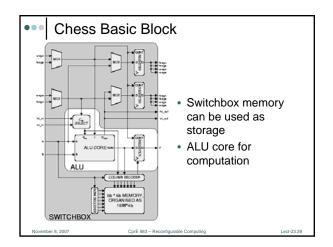

## ••• Chess

- HP Labs Bristol, England

- 2-D array similar to Matrix

- Contains more "FPGA-like" routing resources

- No reported software or application results

CprE 583 - Recon

• Doesn't support incremental compilation

Lect-23.37

## ••• Summary

November 8, 2007

- Architectures moving in the direction of coarse-grained blocks

- Latest trend is functional pipeline

- Communication determined at compile time

Lect-23.4

• Software support still a major issue

CprE 583 - Rec