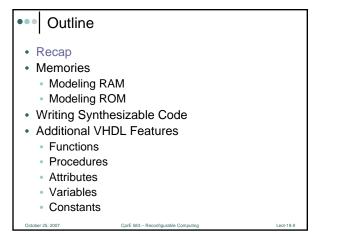

| ••• Gener               | ic RAM (cont.)                                                                                                     |            |

|-------------------------|--------------------------------------------------------------------------------------------------------------------|------------|

| TYPE vector_i<br>STD_LO | E behavioral OF ram IS<br>array IS ARRAY (0 TO words-1) OF<br>GIC_VECTOR(bits – 1 DOWNTO 0);<br>ory: vector array; |            |

| ÌF (clk                 | ,<br>ia='1') THEN<br>EVENT AND clk='1') THEN<br>mory(addr) <= data_in;<br>IF;<br>SS;                               |            |

| October 25, 2007        | CprE 583 - Reconfigurable Computing                                                                                | Lect-19.11 |

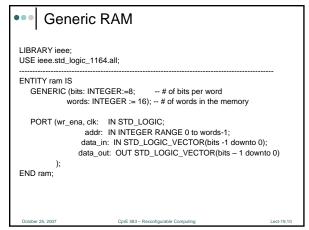

| ••• Ger                       | neric  | ROM                             |                                            |           |

|-------------------------------|--------|---------------------------------|--------------------------------------------|-----------|

| LIBRARY ieee<br>USE ieee.std_ |        | 94.all;                         |                                            |           |

| ENTITY rom I<br>GENERIC       | (bits: |                                 | # of bits per word<br># of words in the me | emory     |

| PORT (<br>);                  |        | IN INTEGER RAN<br>OUT STD_LOGIC | IGE 0 to words-1;<br>C_VECTOR(bits – 1 dow | nto 0)    |

| END rom;                      |        |                                 |                                            |           |

| October 25, 2007              |        | CprE 583 – Reconfigurab         | le Computing                               | ect-19.12 |

# Constants Syntax: CONSTANT name : type := value; Examples: CONSTANT high : STD\_LOGIC := '1'; CONSTANT datamemory : memory := ((X"00", X"02");

## Constants – Features

tober 25, 2007

- Constants can be declared in a PACKAGE, ENTITY, or ARCHITECTURE

- When declared in a PACKAGE, the constant is truly global, for the package can be used in several entities

- When declared in an ARCHITECTURE, the constant is local, i.e., it is visible only within this architecture

- When declared in an ENTITY, the constant can be used in all architectures associated with this entity

CprE 583 - Reconfigurable Compu

Lect-19.1

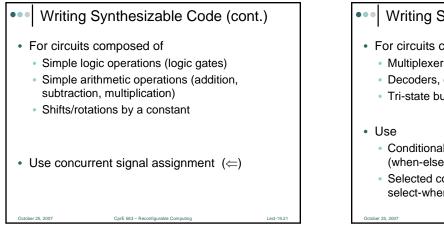

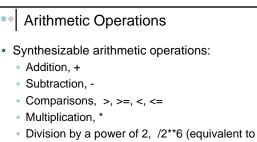

### ••• Writing Synthesizable Code

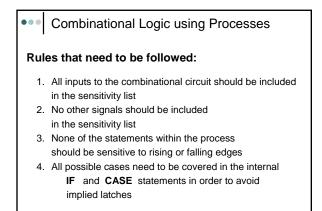

- For combinational logic, use only concurrent statements

- Concurrent signal assignment (⇐)

ber 25, 2007

- Conditional concurrent signal assignment (when-else)

- Selected concurrent signal assignment (withselect-when)

- · Generate scheme for equations (for-generate)

CprE 583 - Reconfig

- Division by a power of 2, /2\*\*6 (equivalent to right shift)

- Shifts by a constant, SHL, SHR

CprE 583 - Reconfi

October 25, 2007

### Arithmetic Operations (cont.)

· The result of synthesis of an arithmetic operation is a

- Combinational circuit

- Without pipelining

r 25, 2007

The exact internal architecture used (and thus delay and area of the circuit) may depend on the timing constraints specified during synthesis (e.g., the requested maximum clock frequency)

CprE 583 - Reconfigurable Co

CprE 583 - Reconfigurable Comp

October 25, 2007

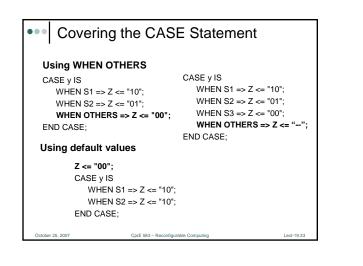

# ••• Covering the IF Statement Using ELSE IF A = B THEN AeqB <= '1'; ELSE AeqB <= '0'; Using default values AeqB <= '0'; IF A = B THEN AeqB <= '1';

| ••• Initializa                           | ations                                                                                                                                                 |            |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| values, such<br>SIGNAL<br>• Cannot be sy | of signals (and variables) with ini<br>as<br>. a : STD_LOGIC <b>:= '0';</b><br>ynthesized, and thus should be av<br>ey will be ignored by the synthesi | voided     |

| Use set and i                            | reset signals instead                                                                                                                                  |            |

| October 25, 2007                         | CprE 583 – Reconfigurable Computing                                                                                                                    | Lect-19.34 |

#### Variables – Features

r 25, 200

- Can only be declared within processes and subprograms (functions & procedures)

- Initial value can be explicitly specified in the declaration

- When assigned take an assigned value immediately

- Variable assignments represent the desired behavior, not the structure of the circuit

- Should be avoided, or at least used with caution in a synthesizable code

CprE 583 - Recon

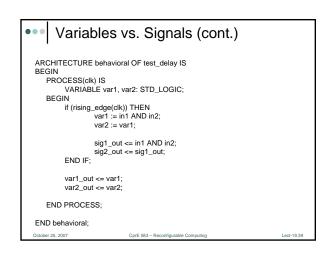

## Variables vs. Signals LIBRARY IEEE; USE IEEE.STD\_LOGIC\_1164.all; ENTITY test\_delay IS PORT( clk : IN STD\_LOGIC; in1, in2 : IN STD\_LOGIC; in1, in2 : IN STD\_LOGIC; isg1\_out : BUFFER STD\_LOGIC; sig1\_out : BUFFER STD\_LOGIC; sig2\_out : OUT STD\_LOGIC; j; END test\_delay;

#### Assert Statements

- Assert is a non-synthesizable statement whose purpose is to write out messages on the screen when problems are found during simulation

- Depending on the **severity of the problem**, the simulator is instructed to continue simulation or halt

- · Syntax:

October 25, 200

- ASSERT condition [REPORT "message"] [SEVERITY severity\_level ];

- The message is written when the condition is FALSE

- Severity\_level can be: Note, Warning, Error (default), or Failure

CorE 583 - Rec

#### Subprograms

- · Include functions and procedures

- Commonly used pieces of code

- · Can be placed in a library, and then reused and shared among various projects

- Use only sequential statements, the same as processes

- · Example uses:

ober 25, 2007

· Abstract operations that are repeatedly performed

CprE 583 - Reconfigurable Co

Type conversions

#### Functions – Basic Features •••

Always return a single value as a result

October 25, 2007

Lect-19.43

- Are called using formal and actual parameters the same way as components •

- Never modify parameters passed to them •

- Parameters can only be constants (including generics) and signals (including ports); •

- Variables are not allowed; the default is a CONSTANT •

- When passing parameters, no range specification should be included (for example no RANGE for INTEGERS, or TO/DOWNTO for STD\_LOGIC\_VECTOR)

- Are always used in some expression, and not called on their own

CprE 583 - Reconfigurable Compu

Lect-19.44

|                               | on Syntax and Example                            |  |

|-------------------------------|--------------------------------------------------|--|

|                               | nction_name ( <parameter_list>)</parameter_list> |  |

| RETURN data_                  |                                                  |  |

| [declarations                 | 6]                                               |  |

| BEGIN                         |                                                  |  |

| (sequential st                | tatements)                                       |  |

| END function_r                | name;                                            |  |

| FUNCTION f1<br>(a, b: INTEGEI | R; SIGNAL c: STD_LOGIC_VECTOR)                   |  |

|                               | LEAN IS                                          |  |

| BEGIN                         |                                                  |  |

| (sequential st                | tatements)                                       |  |

|                               |                                                  |  |

| END f1;                       |                                                  |  |

| ••• Procedu                                                                                                                                                  | ires – Basic Features               | 3                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------|

| same way as<br>May modify pa<br>Each parameters ca<br>signals (include<br>The default for<br>default for out<br>When passing<br>be included (fr<br>TO/DOWNTO | ng formal and actual parame         | UT, INOUT<br>enerics),<br>ant, the<br>s a variable<br>ation should<br>:GERS, and |

| October 25, 2007                                                                                                                                             | CprE 583 - Reconfigurable Computing | Lect-19.46                                                                       |

| •••    | Procedure Syntax and Example                                                       |            |

|--------|------------------------------------------------------------------------------------|------------|

|        | ROCEDURE procedure_name ( <parameter_list>) IS<br/>[declarations]</parameter_list> |            |

| BE     | EGIN                                                                               |            |

|        | (sequential statements)                                                            |            |

| E      | ND procedure_name;                                                                 |            |

|        |                                                                                    |            |

| PF     | ROCEDURE p1                                                                        |            |

| (a     | a, b: in INTEGER; SIGNAL c: out STD_LOGIC_VECTO                                    | DR)        |

|        | [declarations]                                                                     |            |

| BE     | EGIN                                                                               |            |

|        | (sequential statements)                                                            |            |

| E      | ND p1;                                                                             |            |

| Octobe | er 25, 2007 CprE 583 – Reconfigurable Computing I                                  | .ect-19.47 |

|        |                                                                                    |            |