CprE 583 - Reconfigurable Computi

## ••• Design Exercise

- Design a simple 32-bit CPU

- · Requirements

- Three instruction types: load/store, register ALU, branch-if-equal

- 8 32-bit registers

- ALU operations: ADD, SUB, OR, XOR, AND, CMP

- Memory operations: load word, store word

CprE 583 - Reconf

- Components

- Instruction memory / decode

- Register file

- ALU

October 23, 200

- Data memory

- Other control

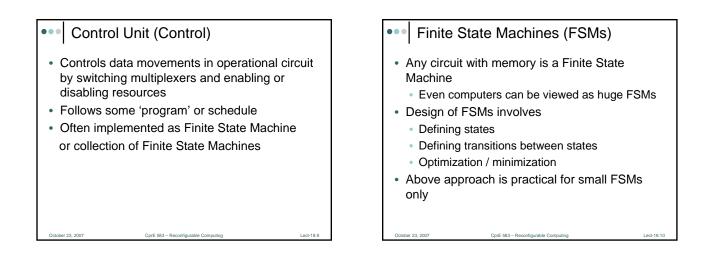

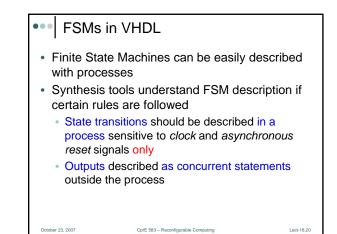

## Outline

- Recap

- Finite State Machines

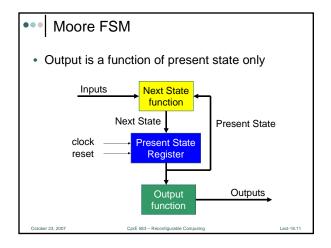

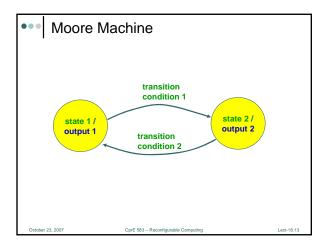

- Moore Machines

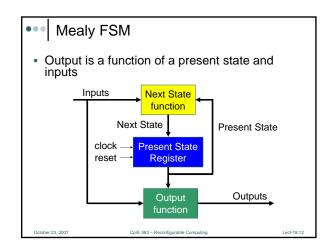

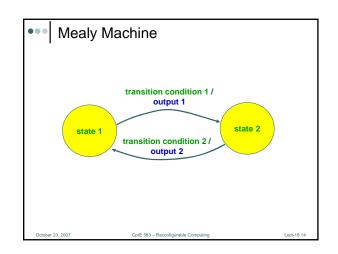

- Mealy Machines

- FSMs in VHDL

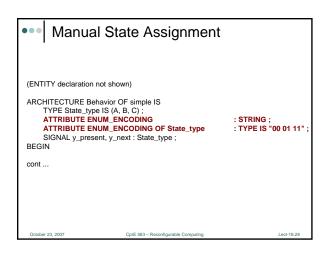

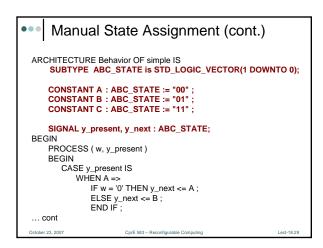

- State Encoding

- Example Systems

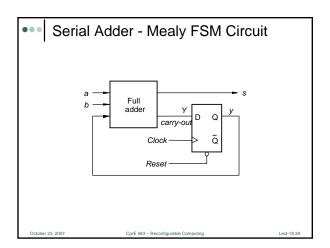

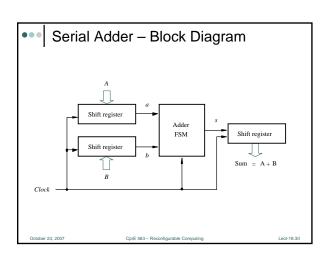

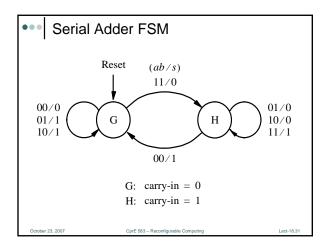

- Serial Adder

October 23, 2007

Lect-18.5

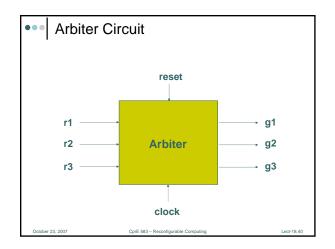

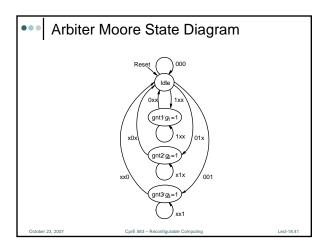

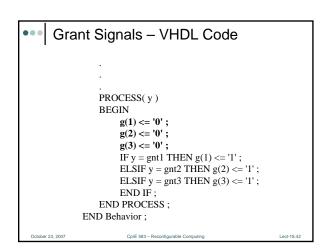

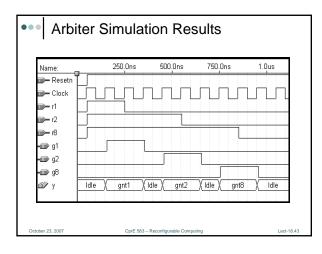

Arbiter Circuit

1

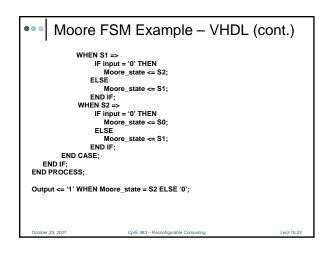

| ••• Moore                                            | FSM Example – VHD                                          | L          |

|------------------------------------------------------|------------------------------------------------------------|------------|

| TYPE state IS (S0,<br>SIGNAL Moore_sta               |                                                            |            |

| CASE Moore<br>WHEN S0<br>IF input =<br>Moore<br>ELSE | /HEN<br>/= <50;<br>/1/ AND clock'event) THEN<br>ø_state IS |            |

| October 23, 2007                                     | CprE 583 – Reconfigurable Computing                        | Lect-18.21 |

## State Encoding Problem

- State encoding can have a big influence on optimality of the FSM implementation

- No methods other than checking all possible encodings are known to produce optimal circuit

- Feasible for small circuits only

ber 23, 2007

Using enumerated types for states in VHDL leaves encoding problem for synthesis tool

CprE 583 - Reconfig

## Types of State Encodings

- Binary (Sequential) States encoded as consecutive binary numbers

- Small number of used flip-flops

- Potentially complex transition functions leading to slow implementations

- · One-Hot only one bit is active

ber 23, 2007

Number of used flip-flops as big as number of states

CprE 583 - Reconfigurable Corr

Lect-18.2

- Simple and fast transition functions

- Preferable coding technique in FPGAs

| State | Binary Code | One-Hot Code |

|-------|-------------|--------------|

| S0    | 000         | 1000000      |

| S1    | 001         | 0100000      |

| S2    | 010         | 00100000     |

| S3    | 011         | 00010000     |

| S4    | 100         | 00001000     |

| S5    | 101         | 00000100     |

| S6    | 110         | 00000010     |

| S7    | 111         | 0000001      |

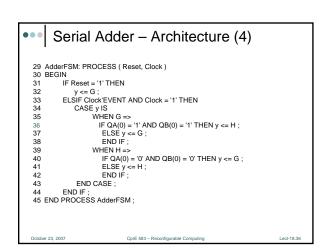

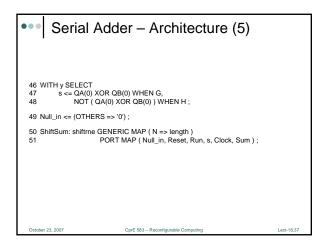

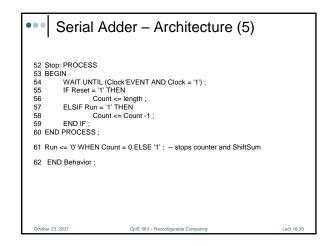

| •••  Se          | rial A           | dder       | FS       | M         | - 5       | sta    | te | lat | ble |            |

|------------------|------------------|------------|----------|-----------|-----------|--------|----|-----|-----|------------|

|                  | Present<br>state | Next state |          |           | Output s  |        |    |     |     |            |

|                  |                  | ab =00     | 01       | 10        | 11        | 00     | 01 | 10  | 11  |            |

|                  | G                | G          | G        | G         | Н         | 0      | 1  | 1   | 0   |            |

|                  | Н                | G          | Н        | Н         | Η         | 1      | 0  | 0   | 1   |            |

|                  |                  |            |          |           |           |        |    |     |     |            |

| October 23, 2007 |                  | CprE       | 583 – Re | configura | able Corr | puting |    |     |     | Lect-18.32 |

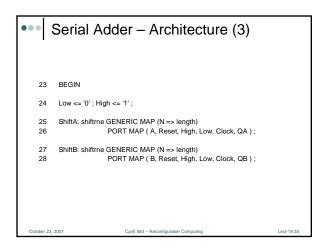

| 10 A                                   | RCHITECTURE Behavior OF serial IS                                                                                                                                                                                       |            |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 11<br>12<br>13<br>14<br>15<br>16<br>17 | COMPONENT shiftme<br>GENERIC ( N : INTEGER := 4 ) ;<br>PORT ( R : IN STD_LOGIC_VECTOR(N-1 DOWNTO 0) ;<br>L, E, w : IN STD_LOGIC ;<br>Clock : IN STD_LOGIC ;<br>Q : BUFFER STD_LOGIC_VECTOR(N-1 DOWNT<br>END COMPONENT ; | Ō 0) ) ;   |

| 18 S                                   | IGNAL QA, QB, Null_in : STD_LOGIC_VECTOR(length-1 DOWNTO 0)                                                                                                                                                             | ;          |

| 19 S                                   | IGNAL s, Low, High, Run : STD_LOGIC ;                                                                                                                                                                                   |            |

| 20 S                                   | IGNAL Count : INTEGER RANGE 0 TO length ;                                                                                                                                                                               |            |

|                                        | YPE State_type IS (G, H) ;<br>IGNAL y : State_type ;                                                                                                                                                                    |            |

|                                        | 23, 2007 CprE 583 - Reconfigurable Computing                                                                                                                                                                            | Lect-18.34 |