# CprE / ComS 583 Reconfigurable Computing Prof. Joseph Zambreno Department of Electrical and Computer Engineering lowa State University Lecture #11 – Logic Emulation Technology

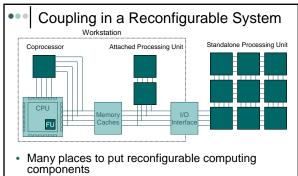

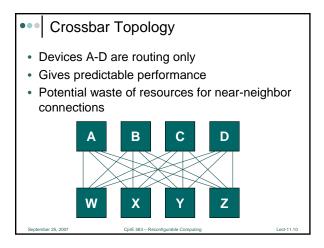

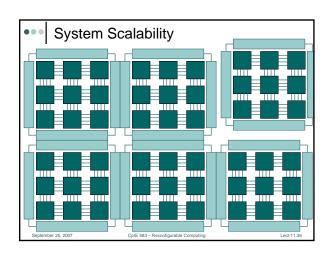

- · Most implementations involve multiple discrete devices

- · How should these devices be connected together?

Modern Multi-FPGA Systems

- · Large logic capacity

- All projects end up pushing capacity limits

- · Large amount of on-board RAM

- · High speed and high density

- To support genome, vision and pharmacological apps

- High speed FPGA-FPGA connections

- To make multiple FPGAs more like one big FPGA

- · Inter-chip connectivity an issue

- · Parallel computers in the traditional sense

- Suitable for spatially parallel applications

- Transmogrifier-4, BEE2

CprE 583 – Reconfigurable Com

# ••• Thought Exercise

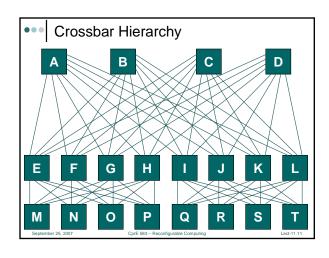

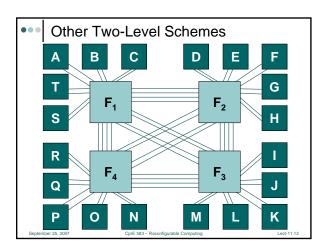

- Consider the linear array, mesh, crossbar, hierarchy, and other two-level topologies

- In groups of 2, analyze the average distance needed to communicate given a random placement of functions to FPGAs

- Can this be represented as a function of N?

- · Assume finite number of pins per device

- · Best topology wins a prize

Contombor 2E 2003

CorE E83 Reconfigurable Computing

Lect-11.13

# Bipartitioning

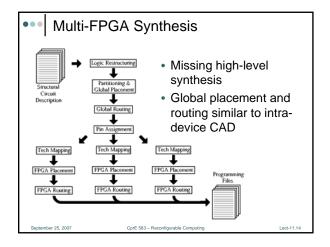

- Perhaps biggest problem in multi-FPGA design is partitioning

- · NP-complete for general graphs

- Many heuristics/attacks

- Partitioner must deal with logic and pin constraints

- Better to recursively bipartition circuit

September 25, 200

CprE 583 – Reconfigurable Computing

Lect-11.15

# ••• KL FM Partitioning Heuristic

- KLFM Fiduccia-Mattheyses (Kernighan-Lin refinement)

- Greedy, iterative

- · Pick cell that decreases cut and move it

- Repeat

- · Small amount of

- · Look past moves that make locally worse

- Randomization

September 25, 20

CprE 583 – Reconfigurable Computing

Lect-11.1

# ••• KL FM Algorithm

- · Randomly partition into two halves

- · Repeat until no updates

- Start with all cells free

- Repeat until no cells free

- Move cell with largest gain (balance allows)

- Update costs of neighbors

- Lock cell in place (record current cost)

- Pick least cost point in previous sequence and use as next starting position

- · Repeat for different random starting points

September 25, 2007

CprE 583 – Reconfigurable Computing

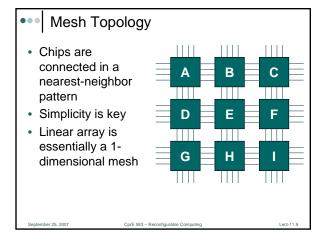

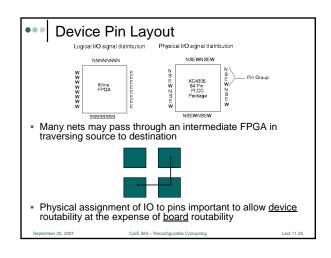

### Problems with Meshes

- Rent's Rule for the number of wires leaving a partition: P = KG<sup>B</sup>

- Perimeter grows as G<sup>0.5</sup> but unfortunately most circuits grow at G<sup>B</sup> where B > 0.5

- · Effectively devices highly pin limited

- · What does this mean for meshes?

| Not Limited  - unused FPGA pins  - unused FPGA gates | Gate Limited  - some unused pins  - no unused gates |

|------------------------------------------------------|-----------------------------------------------------|

| Pin Limited  - no unused pins - some unused gates    | Balanced  - no unused pins  - no unused gates       |

583 – Reconfigurable Computing

# ••• Multi-FPGA Systems

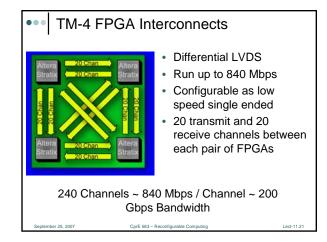

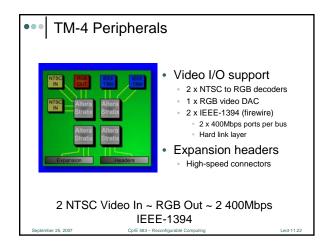

- Transmogrifier-4 (University of Toronto)

- Four Altera Stratix EP1S80F1508C6 FPGAs, each with:

- 79,040 LUTs

- 7.4Mb internal block RAM

- 176 9x9 MACs (4 9x9's can become 1 36x36)

- 1508 pin flip chips

- Total TM-4 Capacity:

- 316,160 Luts

- 29.6Mb internal block RAM

- 704 9x9 MACs

September 25, 2007

CprE 583 - Reconfigurable Computing

Transmogrifier-4 Gigabit Etherne 64/66Mhz 1.2GHz 2xNTSC Video IEEE 32GB 1394 **DDR** SDRAM 840Mbps Altera Stratix LVDS Ports S80 FPGA

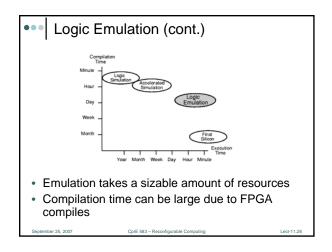

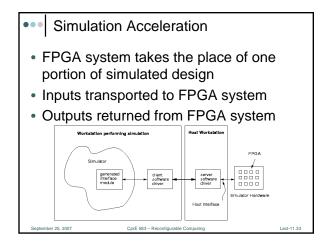

# Logic Emulation

- Custom ASIC circuits \$\$\$

- ASIC designers want to ensure that the circuit is correct before final stages of design

- Software simulation?

- Logic emulation circuit is mapped onto a multi-FPGA system

- Several orders of magnitude faster than software simulation

- · The original "killer app" for FPGAs

September 25, 200

CprE 583 – Reconfigurable Computing

Lect-11.27

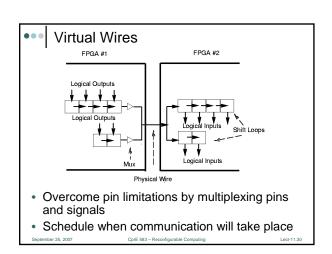

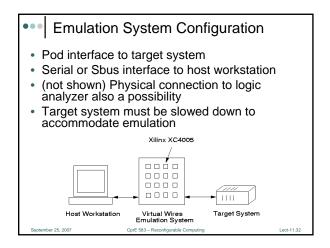

# Example System: Virtual Wires

- Goal is to take an ASIC design and map it to multi-FPGA hardware

- Can replace new chip in target system to allow for software development

- · Important issues include

- How is system interfaced to workstation

- What is interface to target system

- How can memory be emulated

- · Logic analysis / debugging

September 25, 2007

CprE 583 – Reconfigurable Computing

Lect-11.29

# Summary

- Most FPGA systems require multiple devices

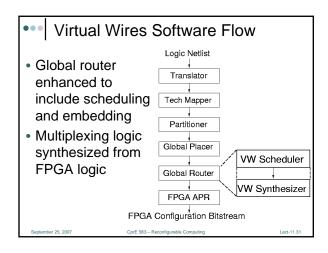

- System software involves many steps

- Bipartitioning has been the subject of much research

- Topologies affect performance and use

- An active area of research as "devices" migrate inside the chip

- One common use of multi-FPGA systems is logic emulation

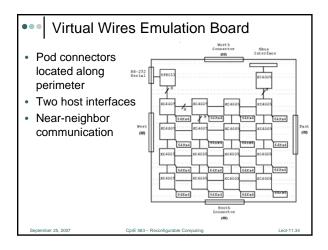

- An example system (virtual wires) uses a near-neighbor mesh with several external interfaces.

- Virtual wires overcome pin limitations by intelligently multiplexing I/O signals

- www.mentor.com/products/fv/emulation/vstation\_pro

www.synplicity.com/products/haps