#### CprE / ComS 583 Reconfigurable Computing

Prof. Joseph Zambreno Department of Electrical and Computer Engineering Iowa State University

Lecture #2 - Comparing Computing Machines

## **Quick Points**

- Course survey posted on WebCT

- Not very anonymous

- · Will do again around the middle of term

- HW #1 will be out by tonight

- Due 1 week from Tuesday (September 4)

- · Will require a couple of concepts introduced next week to be completed

Lect-02.2

· Don't stress out!

August 23, 2007

· Next week Thursday - online only class CprE 583 - Reconfig

Weekly schedule: <u>http://class.ece.iastate.edu/cpre583</u>

CprE 583 - Reconf

- **Course Project**

- · Perform an in-depth exploration of some area of reconfigurable computing

- Whatever topic you choose, you must include a strong experimental element in your project

- Work in groups of 2+ (3 if very lofty proposal)

- · Deliverables:

- Project proposal (2-3 pages, middle of term)

- Project presentation (25 minutes, week 15)

- Project report (10-15 pages, end of term)

CprE 583 - Reconfigurable Computin

| ••• Previous Year's Topics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Fall 2006 projects: <ul> <li>"FPGA Implementation of Frequency-Domain Audio Filter Bank" (2 students)</li> <li>"Transparent FPGA-Based Network Analyzer" (2 students)</li> <li>"FPGA-Based Library Design for Linear Algebra Applications" (2 students)</li> <li>"An Improved Approach of Configuration Compression for FPGA-based Embedded Systems" (2 students)</li> <li>"Analysis of Sobel Edge Detection Implementations" (1 student)</li> <li>"Artificial Neural Networks on Dynamically Reconfigurable FPGAs" (3 students)</li> </ul> </li> </ul> |

| <ul> <li>Papers and presentations for these are available upon request</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| • We can do better!                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

CprE 583 - Reconfi

We can do better!

August 23, 2007

## Recap

ust 23, 2007

### Reconfigurable Computing:

- (1) systems incorporating some form of hardware programmability – customizing how the hardware is used using a number of physical control points [Compton, 2002]

- (2) computing via a post-fabrication and spatially programmed connection of processing elements [Wawrzynek, 2004]

Lect-02.

• (3) general-purpose custom hardware [Goldstein, 1998]

CprE 583 - Reco

Lect-02.

# ••• Design Exercise

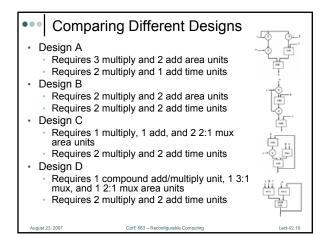

• Consider the function:  $y = Ax^2 + Bx + C$

CprE 583 - Reconf

- In groups of 2, design an architecture for this function

- · Building blocks adders, multipliers, muxes

- Don't worry too much about control or timing

- · Best circuit design wins a prize

August 23, 2007

| ••• Various Possible Designs                                   |          |          |  |  |

|----------------------------------------------------------------|----------|----------|--|--|

| Design A                                                       | Design B | Design C |  |  |

|                                                                |          | Design D |  |  |

| August 23, 2007 CprE 583 – Reconfigurable Computing Lect-02.18 |          |          |  |  |

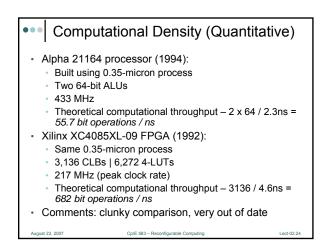

| ••• Computational Density (Quantitative)                                                                                                                                                                                                  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <ul> <li>Intel Pentium 4 "Prescott" processor (2004):</li> <li>Built using 90-nm process</li> <li>2 simple double-speed ALUs, 1 complex single-speed<br/>ALU = approx. 5 32-bit ALUs</li> </ul>                                           |  |  |

| <ul> <li>3.2 GHz</li> <li>Theoretical computational throughput – 5 x 32 / .3125<br/>ns = 512 bit operations / ns</li> <li>Xilinx XC4VLX200 FPGA (2004):</li> </ul>                                                                        |  |  |

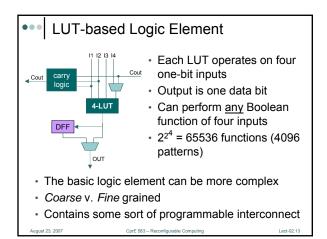

| <ul> <li>Same 90-nm process</li> <li>22,272 CLBs   178,176 4-LUTs</li> <li>500 MHz (peak clock rate)</li> <li>Theoretical computational throughput – 89,088 / 2.0ns = 44,544 bit operations / ns</li> <li>Too good to be true?</li> </ul> |  |  |

|                                                                                                                                                                                                                                           |  |  |

## ••• Notes

- XC4V200 is 87 times faster than Pentium 4?

- · Only simple integer arithmetic

- Division, sqrt, etc.

- Microprocessors have dedicated FP logic

- · How efficiently are resources used?

- Ex: if only 8-bit operations being used, FPGA is an additional 4x more computationally dense than 32-bit CPU

- Challenges making FPGAs run consistently at their peak rate

CprE 583 - Reconfigurable Com

Lect-02.2

· What about cost?

August 23, 2007

#### Summary

August 23, 2007

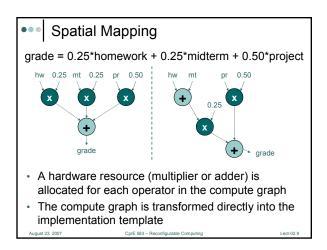

- FPGAs spatial computation

- CPU temporal computation

- FPGAs are by their nature more computationally "dense" than CPU

- In terms of number of computations / time / area

Can be quantitatively measured and compared

- Capacity, cost, ease of programming still important issues

CprE 583 - Reconfigurable Computing

Lect-02.29

Numerous challenges to reconfiguration