# **CprE 2810: Digital Logic**

**Instructor: Alexander Stoytchev**

http://www.ece.iastate.edu/~alexs/classes/

# **Logic Gates**

CprE 2810: Digital Logic Iowa State University, Ames, IA Copyright © Alexander Stoytchev

#### **Administrative Stuff**

- HW1 is out. It is due on Wednesday Sep 3 @ 10pm.

- Submit it as a PDF upload on Canvas before the deadline.

- You can write the solutions on paper and then scan the pages to make \*\*one\*\* PDF file.

- No late homeworks will be accepted.

- Please write clearly on the first page:

- your name

- student ID

- lab section number

#### **Labs Next Week**

- Please download and read the lab assignment for next week before you go to your lab section.

- https://www.ece.iastate.edu/~alexs/classes/2025\_Fall\_2810/labs/Lab\_01/

- You must print and complete the prelab before you go to the lab.

- The TAs will check your prelab answers at the beginning of the recitation. If you don't have it done, you'll lose 20% of the lab grade for that lab.

# CprE 2810: Digital Logic (Fall 2025)

4:25 - 5:15 pm (Mondays, Wednesdays, and Fridays)

Hoover Hall, Room 2055

Instructor: Alexander Stoytchev

- Syllabus

- Class Schedule (Tentative)

- <u>Lecture Notes</u> (also in <u>PDF</u>)

- Labs

- Recitations

- Extra Readings

- Verilog Stuff

- <u>Verilog Reference</u>

- i281 CPU

- <u>i281 CPU Simulator</u>

#### CprE 2810: Digital Logic (Lab Assignments)

- Lab 1

- Lab 2

- Lab 3

- Lab 4

- Lab 5

- Mini Project

- Lab 6

- Lab 7

- Lab 8

- Lab 9

- Lab 10

- Lab 11

- Lab 12

- Lab 13

- Remote Access Instructions

| Name                             | Last modified    | Size |

|----------------------------------|------------------|------|

| Parent Directory                 |                  | _    |

| CPRE281_LAB01(Answer_Sheet).docx | 2021-08-27 14:02 | 26K  |

| CPRE281_LAB01(Answer_Sheet).pdf  | 2021-08-27 14:03 | 338K |

| CPRE281_LAB01.docx               | 2021-08-27 14:04 | 1.9M |

| CPRE281_LAB01.pdf                | 2021-08-27 14:04 | 1.4M |

| lab1.zip                         | 2021-08-27 13:56 | 5.4M |

|                                  |                  |      |

| Name                             | Last modified    | Size |

|----------------------------------|------------------|------|

| Parent Directory                 |                  | _    |

| CPRE281_LAB01(Answer_Sheet).docx | 2021-08-27 14:02 | 26K  |

| CPRE281_LAB01(Answer_Sheet).pdf  | 2021-08-27 14:03 | 338K |

| CPRE281_LAB01.docx               | 2021-08-27 14:04 | 1.9M |

| CPRE281_LAB01.pdf                | 2021-08-27 14:04 | 1.4M |

| <u>lab1.zip</u>                  | 2021-08-27 13:56 | 5.4M |

|                                  |                  |      |

READ one of these at home.

This is the lab assignment.

| Name                             | Last modified    | Size |

|----------------------------------|------------------|------|

| Parent Directory                 |                  | _    |

| CPRE281_LAB01(Answer_Sheet).docx | 2021-08-27 14:02 | 26K  |

| CPRE281_LAB01(Answer_Sheet).pdf  | 2021-08-27 14:03 | 338K |

| CPRE281_LAB01.docx               | 2021-08-27 14:04 | 1.9M |

| CPRE281_LAB01.pdf                | 2021-08-27 14:04 | 1.4M |

| <u>lab1.zip</u>                  | 2021-08-27 13:56 | 5.4M |

During the lab next week, download this ZIP file and follow the instructions.

| Name                             | Last modified    | Size |

|----------------------------------|------------------|------|

| Parent Directory                 |                  | _    |

| CPRE281_LAB01(Answer_Sheet).docx | 2021-08-27 14:02 | 26K  |

| CPRE281_LAB01(Answer_Sheet).pdf  | 2021-08-27 14:03 | 338K |

| CPRE281_LAB01.docx               | 2021-08-27 14:04 | 1.9M |

| CPRE281_LAB01.pdf                | 2021-08-27 14:04 | 1.4M |

| <u>lab1.zip</u>                  | 2021-08-27 13:56 | 5.4M |

Print this file, complete the prelab, and bring it with you to the lab.

| Name                             | Last modified    | Size |

|----------------------------------|------------------|------|

| Parent Directory                 |                  | _    |

| CPRE281_LAB01(Answer_Sheet).docx | 2021-08-27 14:02 | 26K  |

| CPRE281_LAB01(Answer_Sheet).pdf  | 2021-08-27 14:03 | 338K |

| CPRE281_LAB01.docx               | 2021-08-27 14:04 | 1.9M |

| CPRE281_LAB01.pdf                | 2021-08-27 14:04 | 1.4M |

| <u>lab1.zip</u>                  | 2021-08-27 13:56 | 5.4M |

This is the same, but in Word format.

Logic Expression:

#### Lab 1 Answer Sheet

| Name an             | d Student I  | D:                   |                  | Lab Section: |

|---------------------|--------------|----------------------|------------------|--------------|

| Date:               |              |                      |                  |              |

| PRELAB              | :            |                      |                  |              |

| Q1. Fill in         | n the Truth  | Table below for an A | ND gate:         |              |

| Α                   | В            | С                    |                  | Th           |

| 0                   | 0            |                      |                  | 111          |

| _                   |              |                      |                  |              |

| 1                   | 0            |                      |                  |              |

| 1                   | 1            |                      |                  |              |

| Q3. Wha             | t is the nan | ne of the FPGA on th | e DE2-115 board? |              |

| TA Initials         | s:           | _                    |                  |              |

| LAB:<br>2.0 Fill in | the Truth    | Table for lab1step1: |                  |              |

| Α                   | В            | С                    |                  |              |

| 0                   | 0            |                      |                  |              |

| 0                   | 1            |                      |                  |              |

| 1                   | 0            |                      |                  |              |

| 1                   | 1            |                      |                  |              |

|                     |              |                      |                  |              |

This is the prelab for lab #1.

# Cpr E 281 LAB1 ELECTRICAL AND COMPUTER ENGINEERING IOWA STATE UNIVERSITY

#### Lab 1 Answer Sheet

| Quartus     | Simulation <sup>7</sup> | ΓΑ Initials: _       |          | Questa ModelSim TA Initials: |

|-------------|-------------------------|----------------------|----------|------------------------------|

| 4.0 Fill in | the Truth               | Table for <i>lat</i> | b1step2: |                              |

| w           | х                       | Y                    | Z        | ······                       |

| 0           | 0                       | 0                    |          |                              |

| 0           | 0                       |                      |          | :                            |

|             |                         |                      |          |                              |

|             |                         |                      |          |                              |

|             |                         |                      |          |                              |

|             |                         |                      |          |                              |

| 1           | 1                       | 0                    |          |                              |

| 1           | 1                       | 1                    |          |                              |

| 4.0 Fill in | ·                       | Table for <i>lab</i> |          | ·····                        |

| Α           | В                       | С                    | F        | _                            |

|             |                         |                      |          |                              |

|             |                         |                      |          |                              |

| Logic Exp   | ression:                |                      |          |                              |

| TA Initial  | s:                      | _                    |          |                              |

#### CprE 2810: Digital Logic (Lab Assignments)

- <u>Lab 1</u>

- Lab 2

- Lab 3

- Lab 4

- Lab 5

- Mini Project

- Lab 6

- <u>Lab 7</u>

- Lab 8

- Lab 9

- Lab 10

- Lab 11

- Lab 12

- Lab 13

- Remote Access Instructions

### Lab Safety

This class has a substantial hands-on laboratory section. Students will be using expensive, sensitive, and potentially hazardous equipment. Safety in the lab is a number one priority for students and instructors and to ensure a safe laboratory experience, a brief safety presentation will be given during the first lab session. It is mandatory that all students attend this presentation. Moreover, it is expected that students follow any and all posted safety guidelines. All students must sign the <u>lab safety form</u> (posted in the syllabus).

For reference, a copy of the University Laboratory Safety Manual can be found at:

www.ehs.iastate.edu/sites/default/files/uploads/publications/manuals/labsm.pdf

See also the <u>safety page of the ECpE Department</u>:

http://www.ece.iastate.edu/the-department/safety/

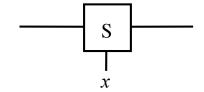

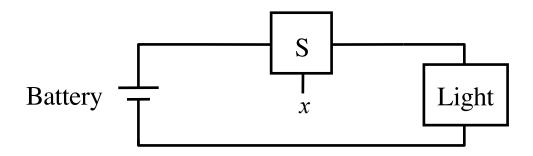

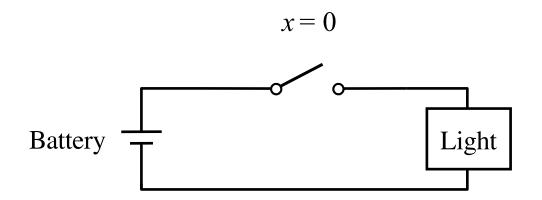

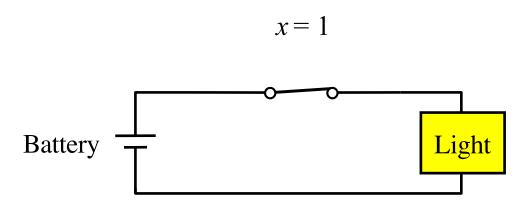

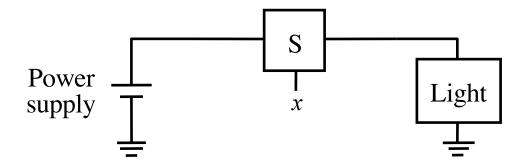

# **A Binary Switch**

(a) Two states of a switch

(b) Symbol for a switch

(a) Simple connection to a battery

(b) Using a ground connection as the return path

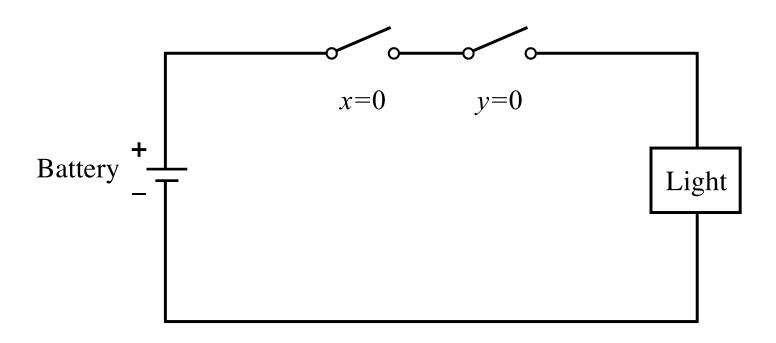

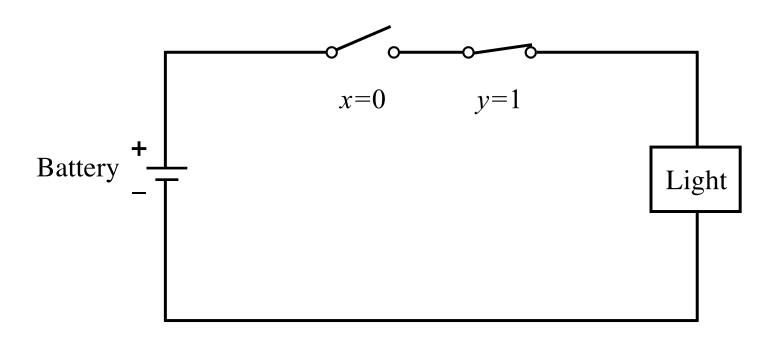

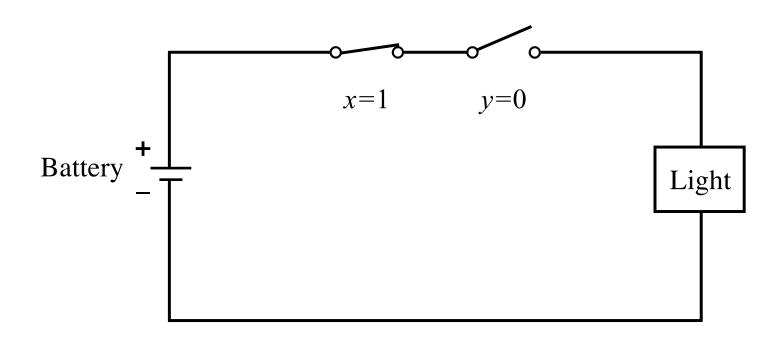

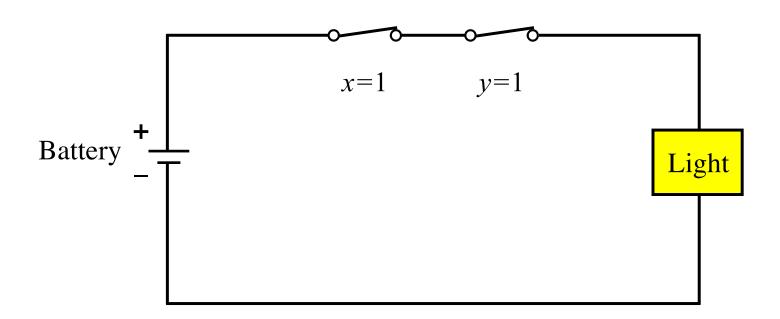

# Logic AND with Switches (series connection of the switches)

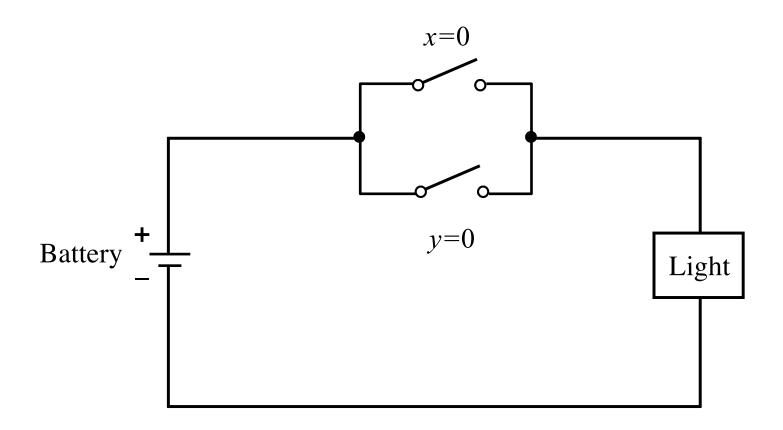

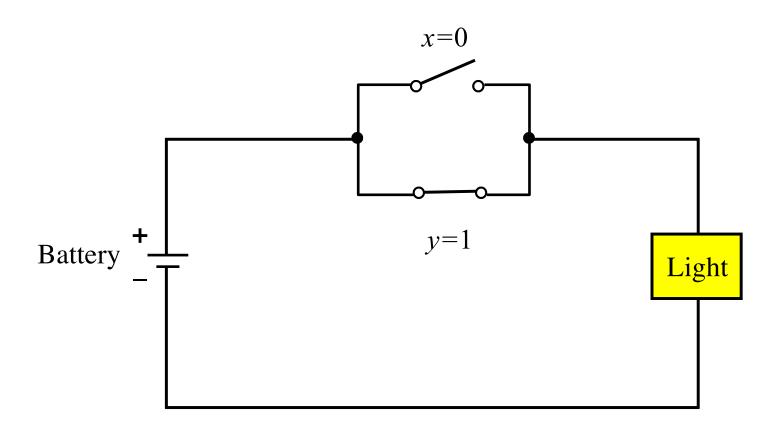

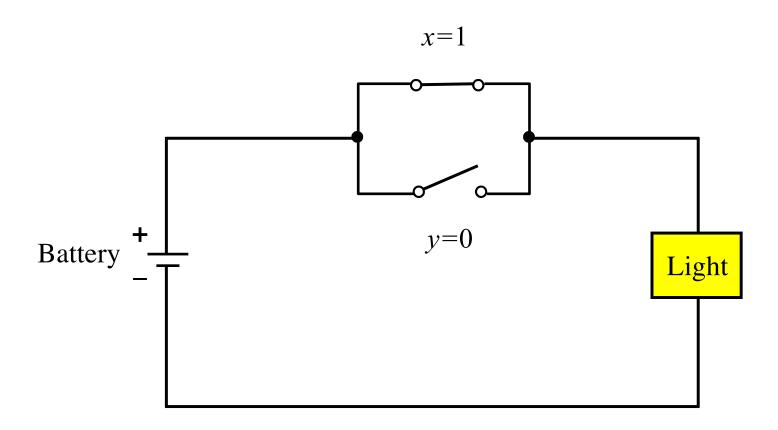

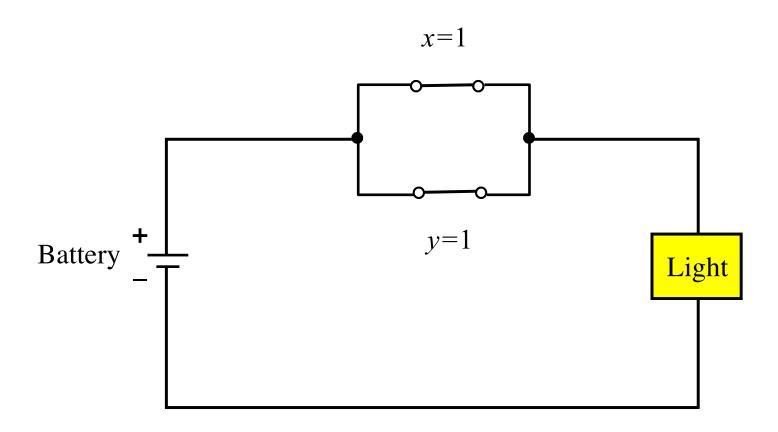

# Logic OR with Switches (parallel connection of the switches)

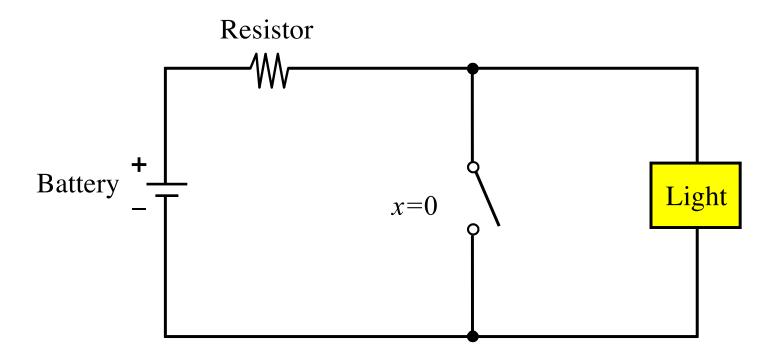

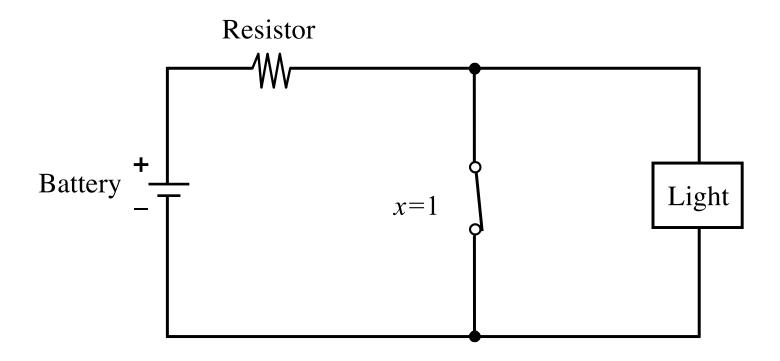

# Logic NOT with a Switch (an inverting circuit)

# **NOT Circuit**

# **NOT Circuit**

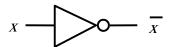

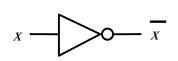

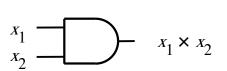

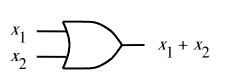

#### The Three Basic Logic Gates

$$x_1$$

$x_2$   $x_1 \times x_2$

$$x_1$$

$x_2$   $x_1 + x_2$

NOT gate

AND gate

OR gate

#### **Truth Table for NOT**

| $\mathcal{X}$ | $\overline{\mathcal{X}}$ |

|---------------|--------------------------|

| 0             | 1                        |

| 1             | 0                        |

#### **Truth Table for AND**

| $x_1$  | $x_2$                                  | $x_1 \cdot x_2$                        |

|--------|----------------------------------------|----------------------------------------|

| 0      | 0<br>1                                 | 0 0                                    |

| 1<br>1 | $\begin{bmatrix} 0 \\ 1 \end{bmatrix}$ | $\begin{vmatrix} 0 \\ 1 \end{vmatrix}$ |

#### **Truth Table for OR**

| $x_1$  | $x_2$  | $x_1 + x_2$ |

|--------|--------|-------------|

| 0      | 0<br>1 | 0           |

| 1<br>1 | 0      | 1 1         |

#### Truth Tables for AND and OR

| $x_1$            | $x_2$            | $x_1 \cdot x_2$ | $x_1 + x_2$      |

|------------------|------------------|-----------------|------------------|

| 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 0<br>0<br>0     | 0<br>1<br>1<br>1 |

AND OR

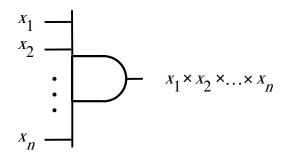

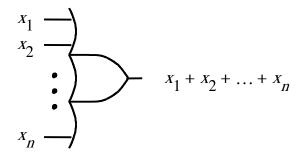

#### **Logic Gates with n Inputs**

AND gate

OR gate

#### **Truth Table for 3-input AND and OR**

| $x_1$ | $x_2$ | $x_3$ | $x_1 \cdot x_2 \cdot x_3$ | $x_1 + x_2 + x_3$ |

|-------|-------|-------|---------------------------|-------------------|

| 0     | 0     | 0     | 0                         | 0                 |

| 0     | 0     | 1     | 0                         | 1                 |

| 0     | 1     | 0     | 0                         | 1                 |

| 0     | 1     | 1     | 0                         | 1                 |

| 1     | 0     | 0     | 0                         | 1                 |

| 1     | 0     | 1     | 0                         | 1                 |

| 1     | 1     | 0     | 0                         | 1                 |

| 1     | 1     | 1     | 1                         | 1                 |

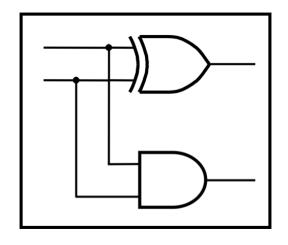

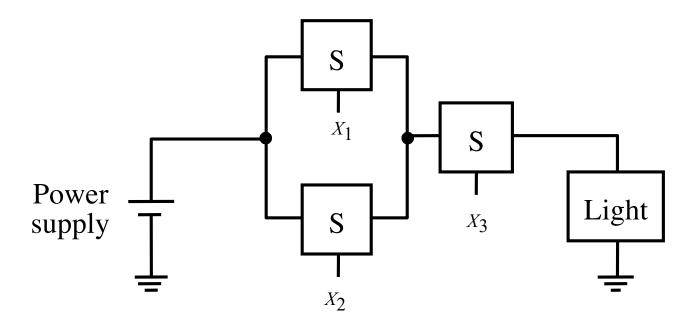

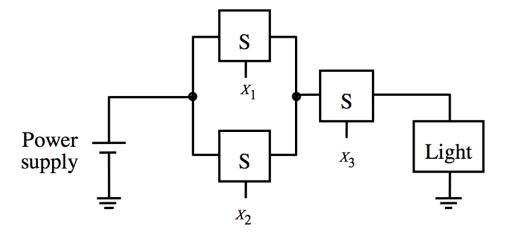

## A series-parallel connection of the switches

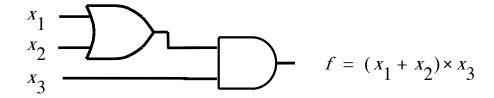

# **Example of a Logic Circuit Implemented with Logic Gates**

$$f = (x_1 + x_2) \times x_3$$

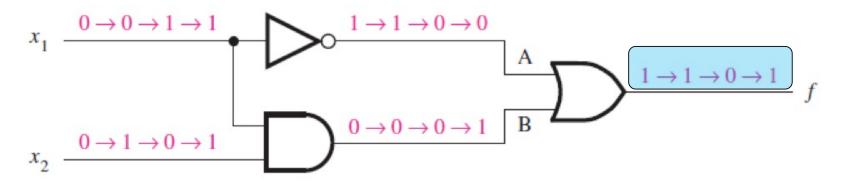

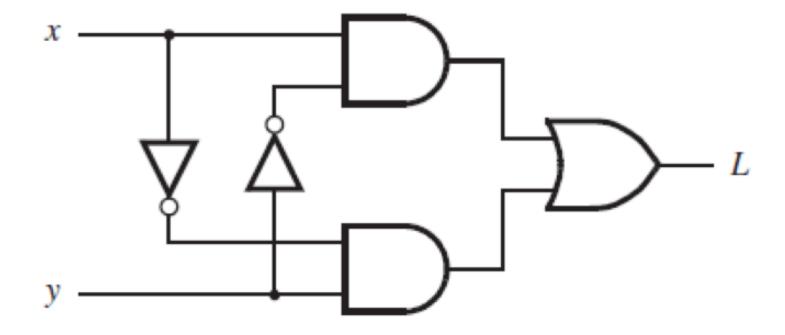

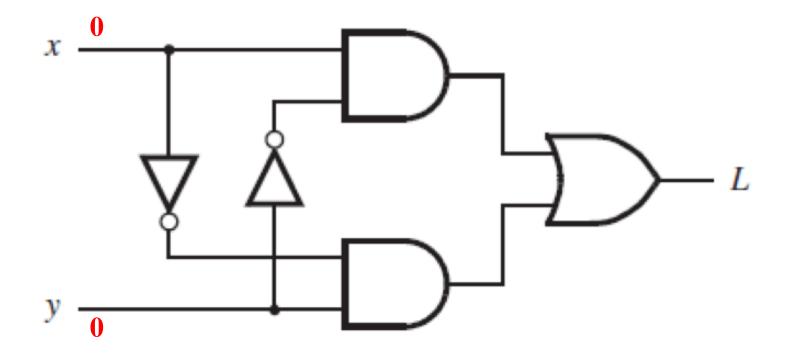

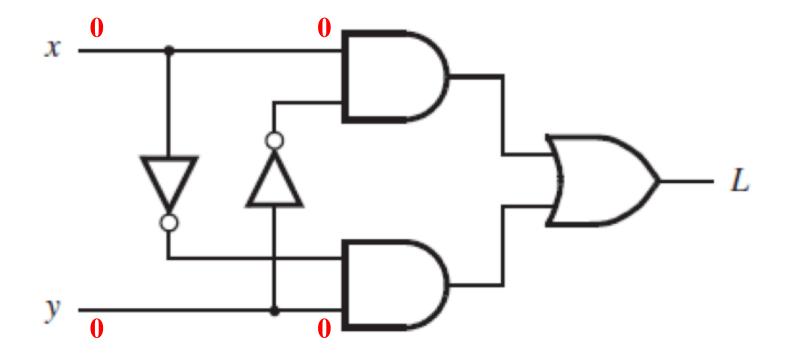

## **Example of a Logic Circuit Implemented with Logic Gates**

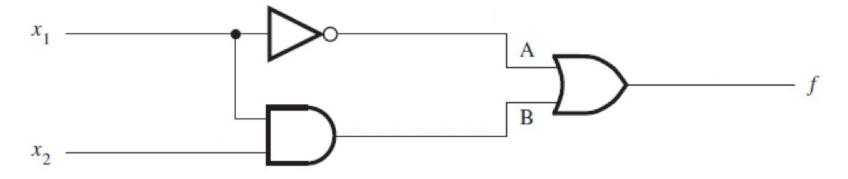

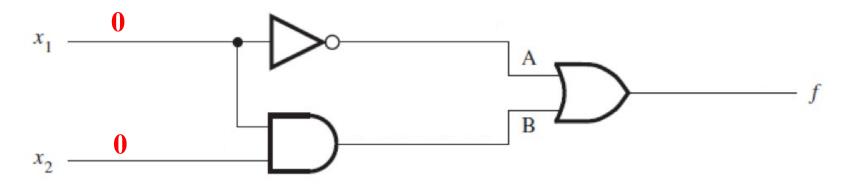

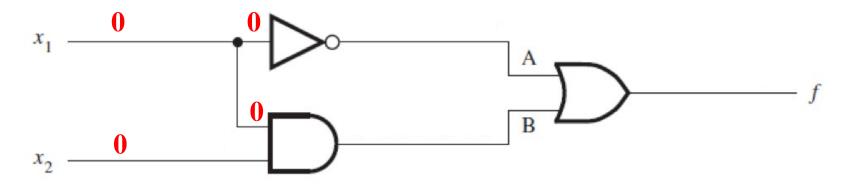

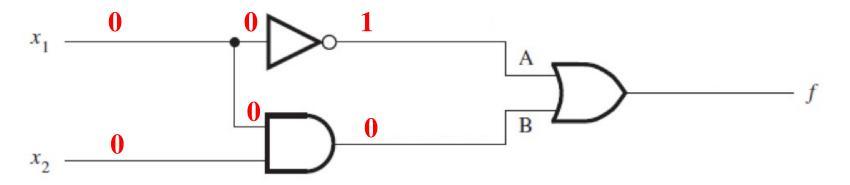

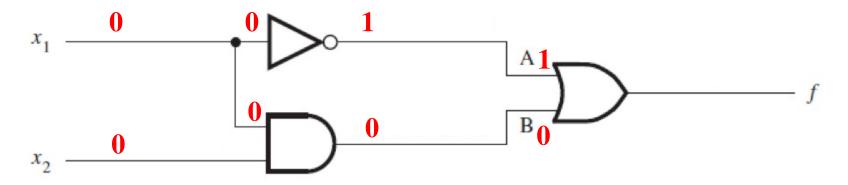

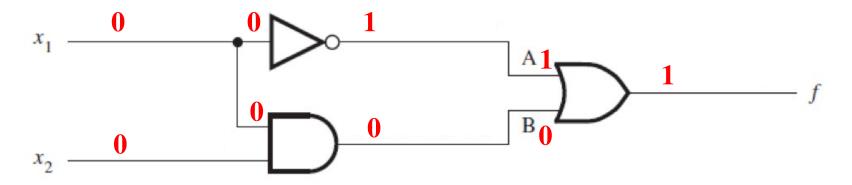

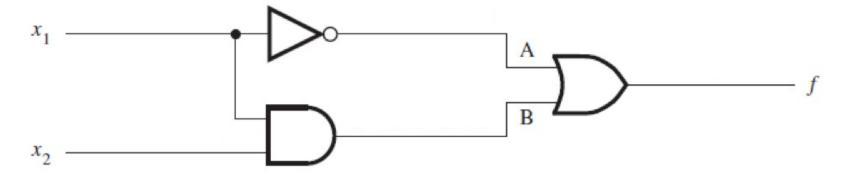

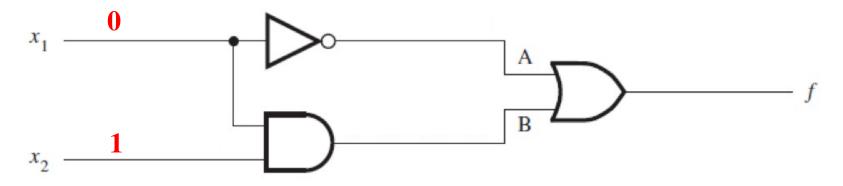

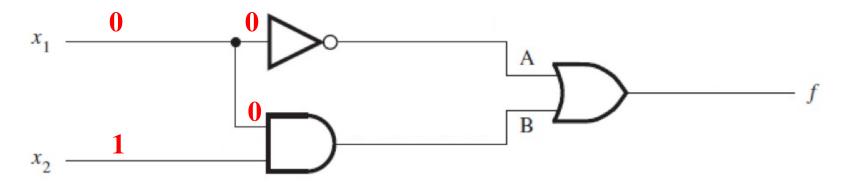

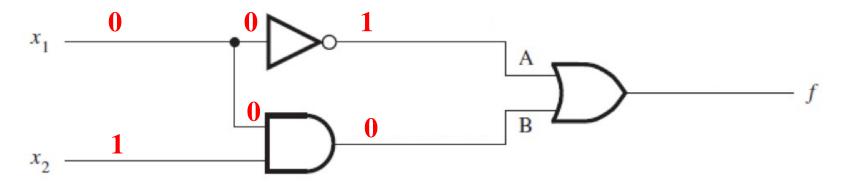

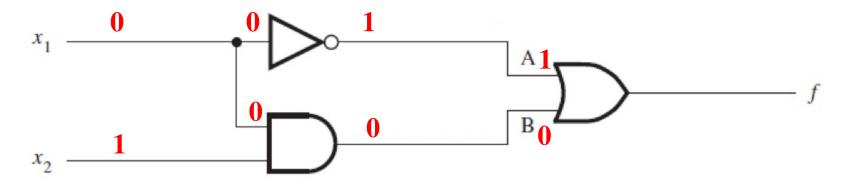

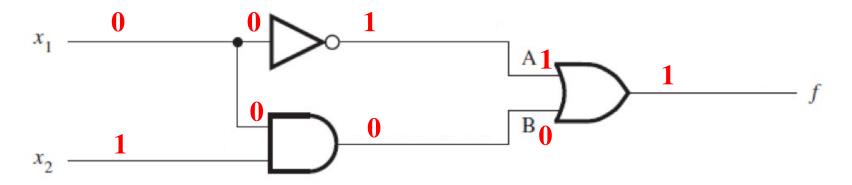

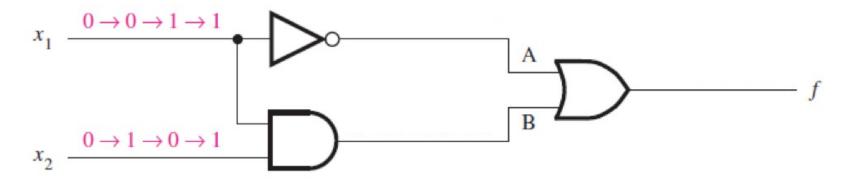

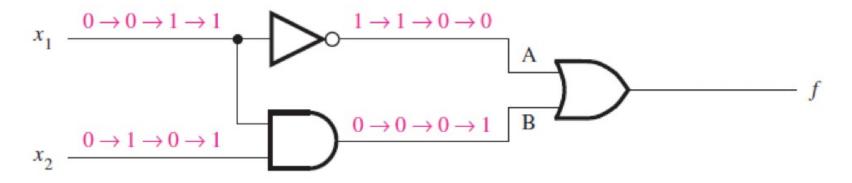

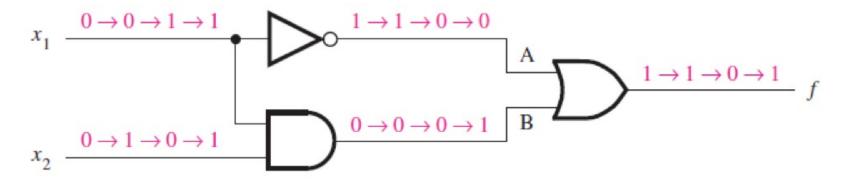

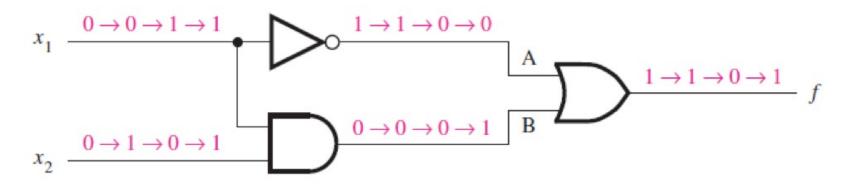

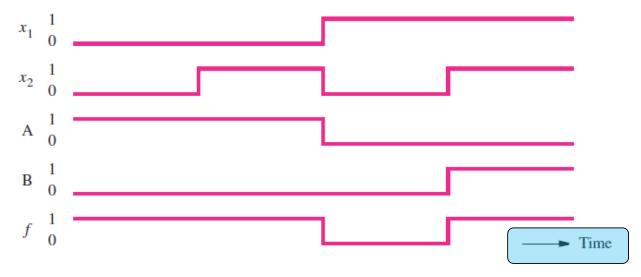

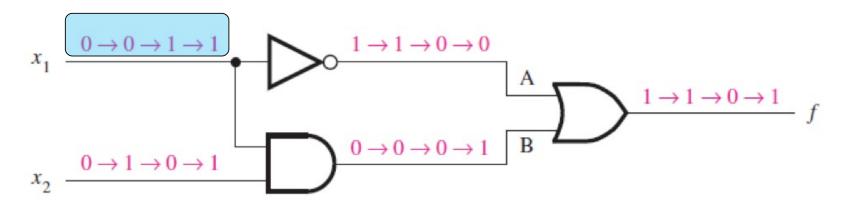

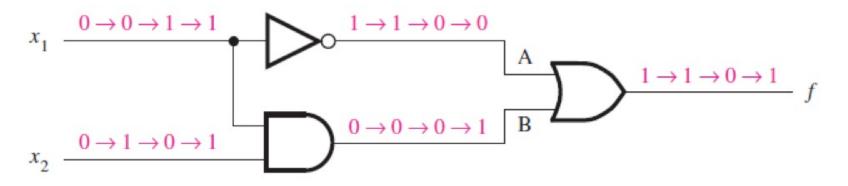

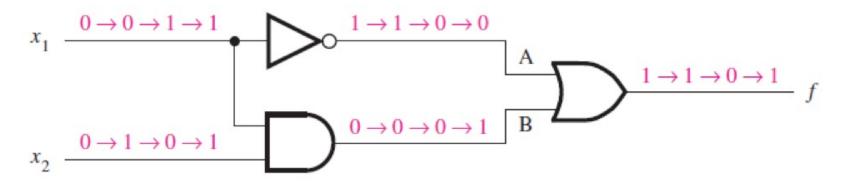

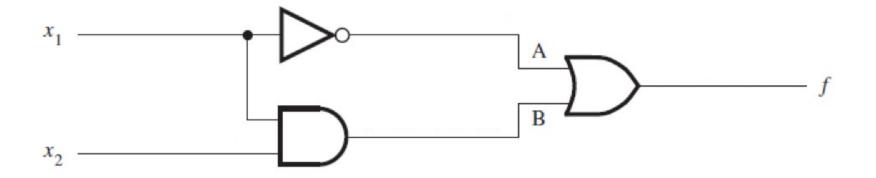

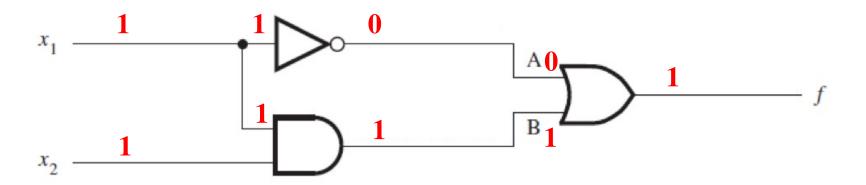

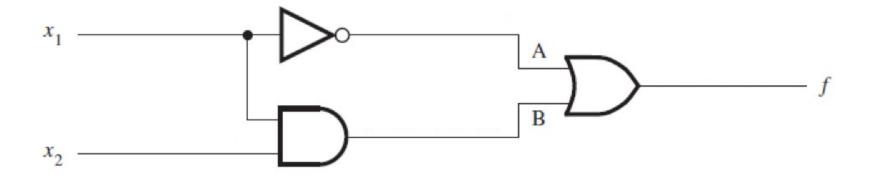

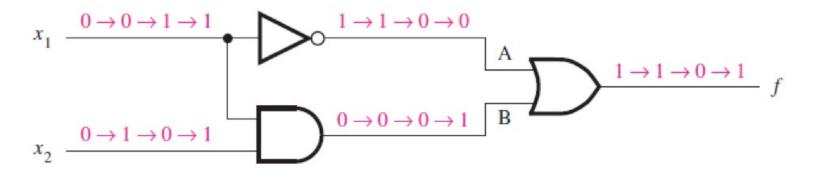

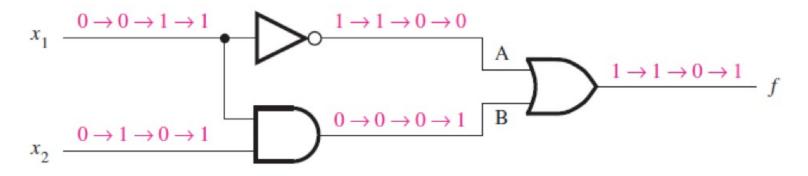

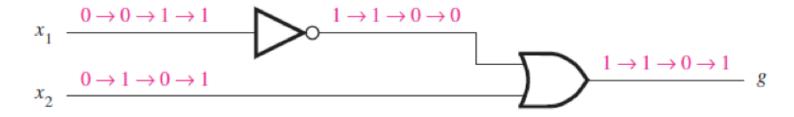

(a) Network that implements  $f = \bar{x}_1 + x_1 \cdot x_2$

[ Figure 2.10 from the textbook ]

[ Figure 2.10 from the textbook ]

[ Figure 2.10 from the textbook ]

[ Figure 2.10 from the textbook ]

[ Figure 2.10 from the textbook ]

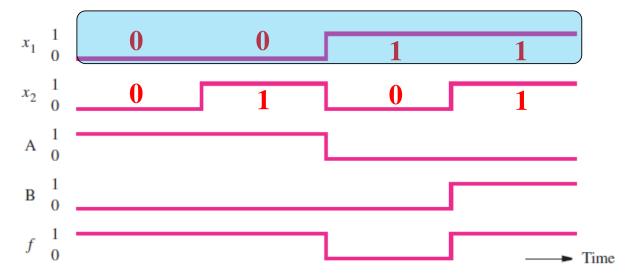

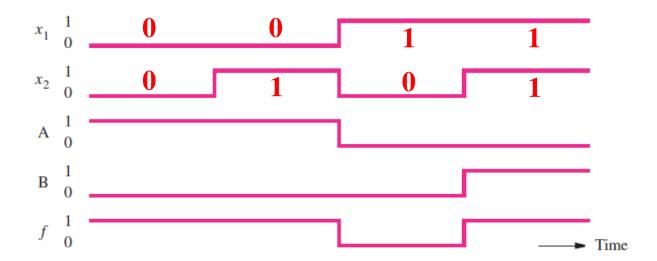

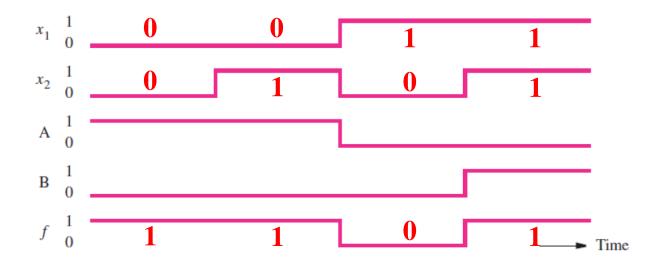

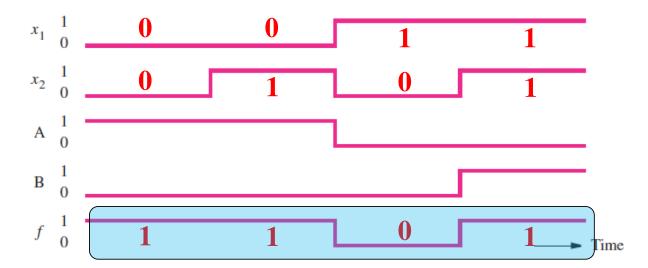

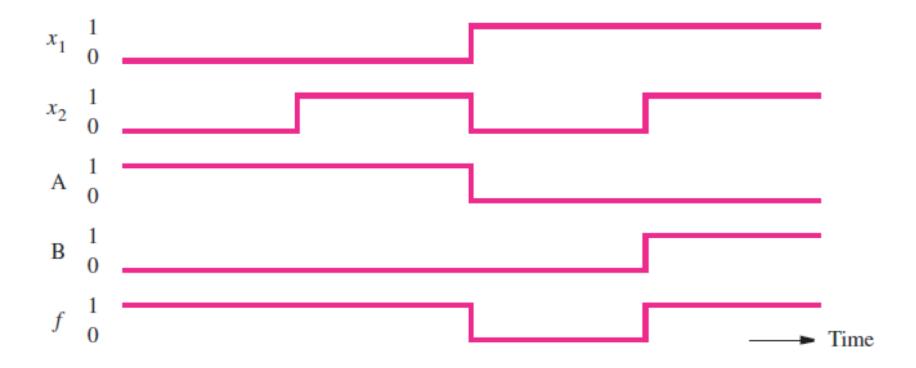

## **Timing Diagram**

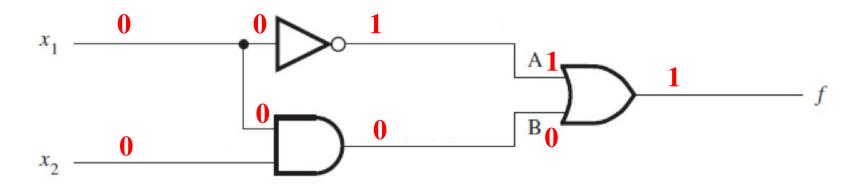

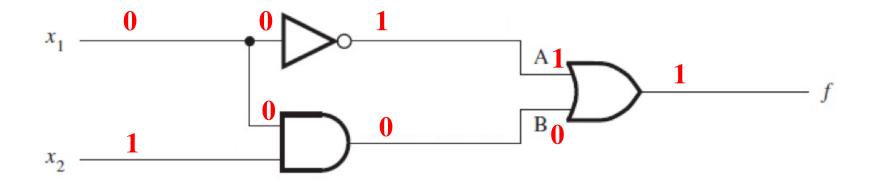

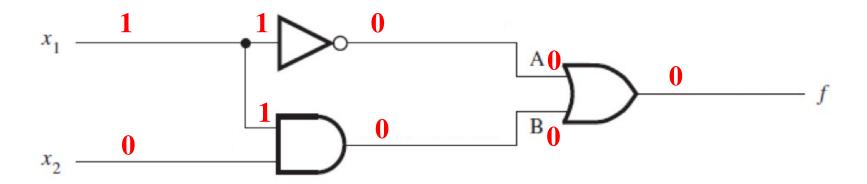

#### **Truth Table for this Logic Circuit**

| 0 0 1 |

|-------|

| 0 1 1 |

| 1 0 0 |

| 1 1 1 |

| $x_1$ | $x_2$ | $f(x_1, x_2)$ |

|-------|-------|---------------|

| 0     | 0     | 1             |

| 0     | 1     | 1             |

| 1     | 0     | 0             |

| 1     | 1     | 1             |

|       |       |               |

| $x_1$ | $x_2$ | $f(x_1, x_2)$ |

|-------|-------|---------------|

| 0     | 0     | 1             |

| 0     | 1     | 1             |

| 1     | 0     | 0             |

| 1     | 1     | 1             |

| $x_1$ | $x_2$ | $f(x_1, x_2)$ |

|-------|-------|---------------|

| 0     | 0     | 1             |

| 0     | 1     | 1             |

| 1     | 0     | 0             |

| 1     | 1     | 1             |

| 0 0 1 |

|-------|

| 0 1 1 |

| 1 0 0 |

| 1 1 1 |

## Truth Table for $f = \overline{x_1} + x_1 x_2$

| $x_1$ | $x_2$ | $f(x_1, x_2)$ |

|-------|-------|---------------|

| 0     | 0     | 1             |

| 0     | 1     | 1             |

| 1     | 0     | 0             |

| 1     | 1     | 1             |

## Truth Table for $f = \overline{x_1} + x_1 x_2$

| $x_1$ | $x_2$ | $f(x_1, x_2)$ |

|-------|-------|---------------|

| 0     | 0     | 1             |

| 0     | 1     | 1             |

| 1     | 0     | 0             |

| 1     | 1     | 1             |

|       |       |               |

## **Functionally Equivalent Circuits**

(a) Network that implements  $f = \bar{x}_1 + x_1 \cdot x_2$

#### **Functionally Equivalent Circuits**

(a) Network that implements  $f = \bar{x}_1 + x_1 \cdot x_2$

(d) Network that implements  $g = \bar{x}_1 + x_2$

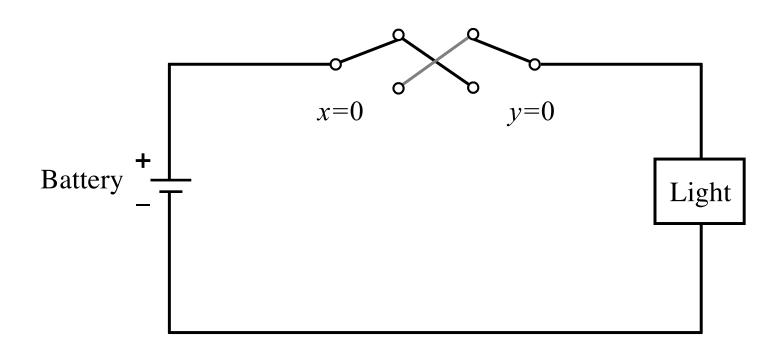

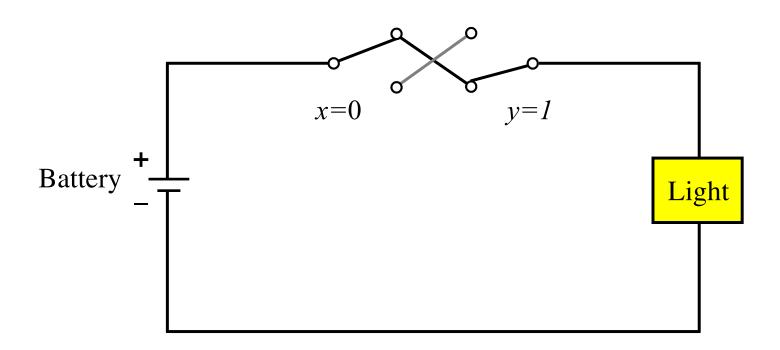

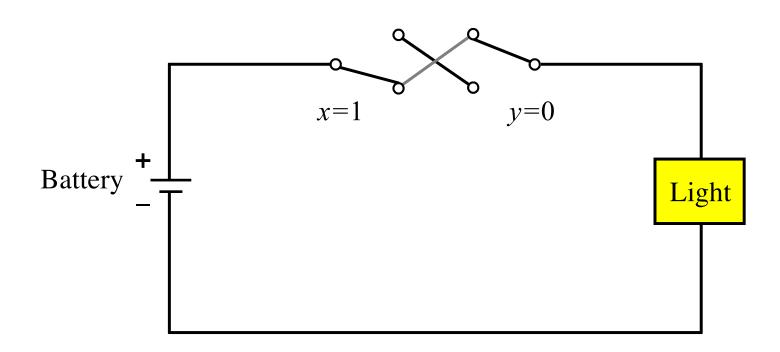

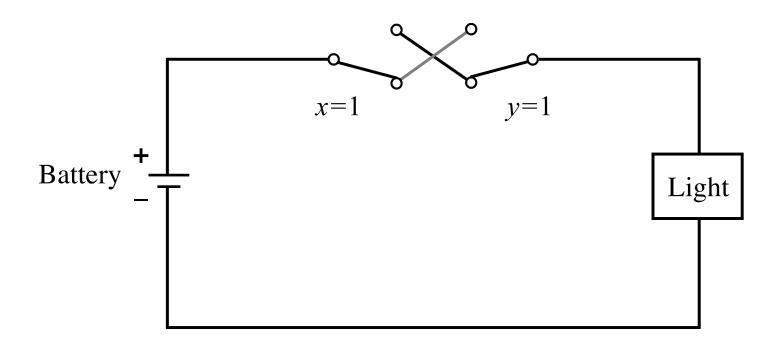

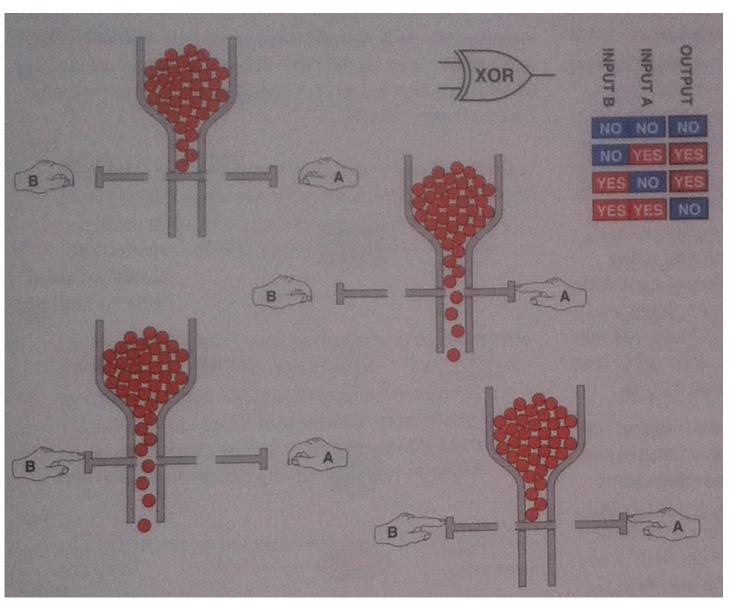

# **Logic XOR with Switches**

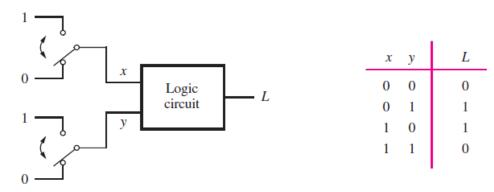

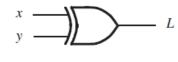

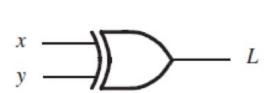

## The XOR Logic Gate

(b) Truth table

## The XOR Logic Gate

| x | y | L |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

|   |   |   |

(a) Two switches that control a light

(b) Truth table

(d) XOR gate symbol

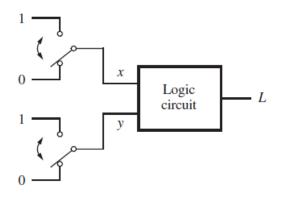

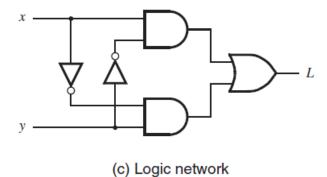

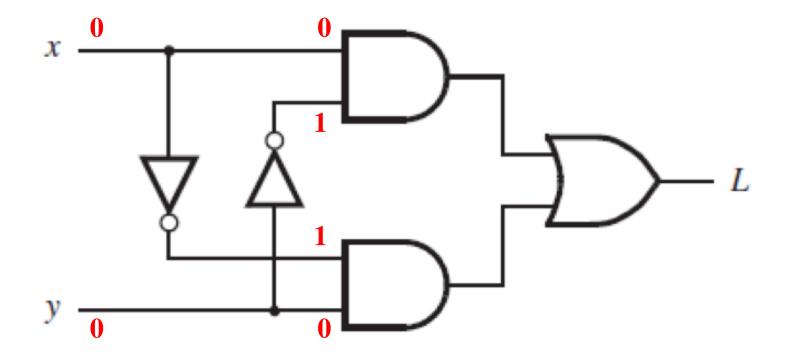

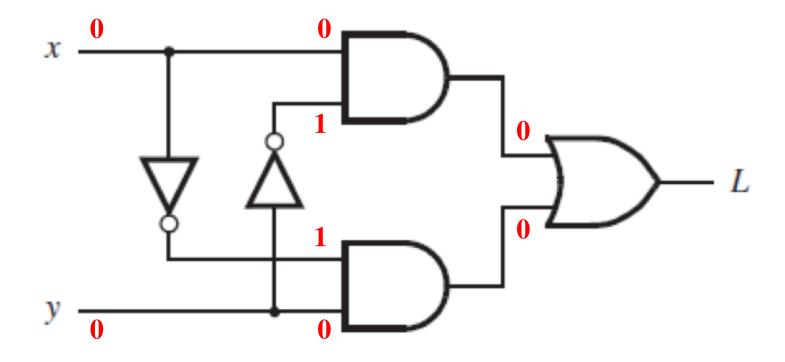

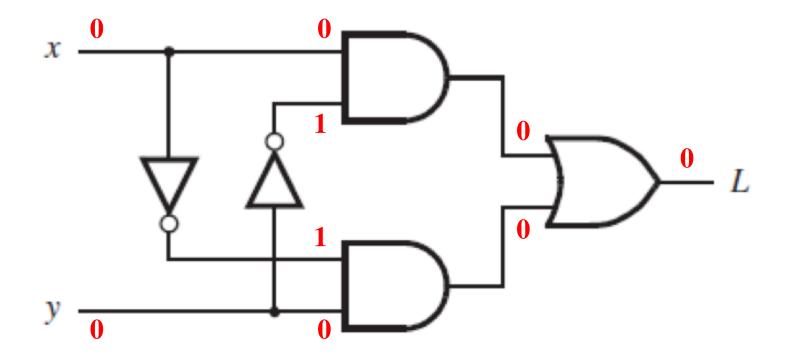

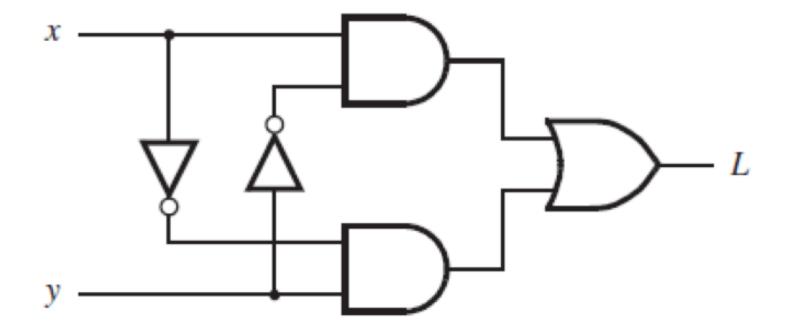

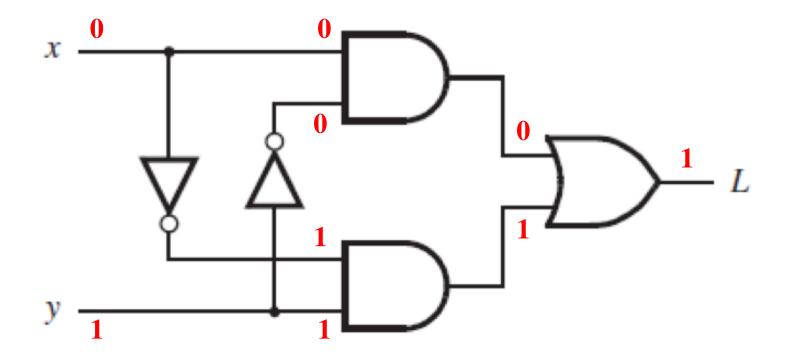

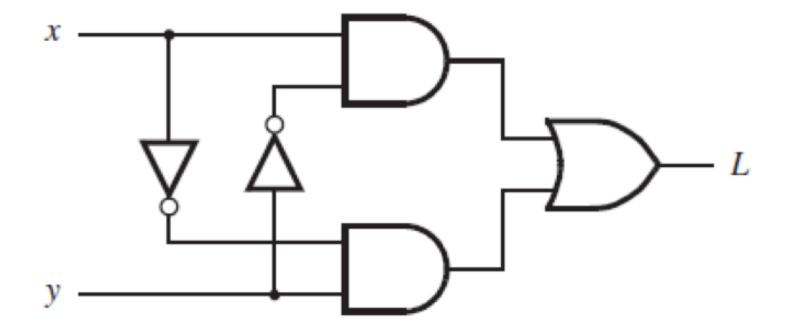

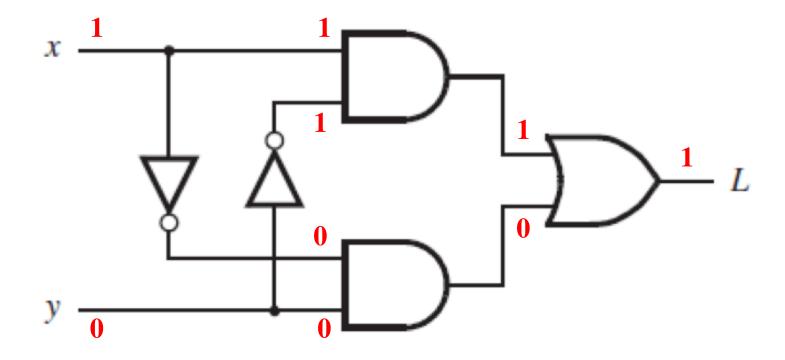

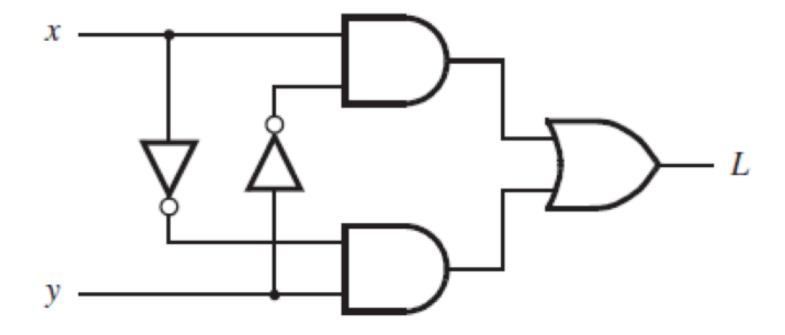

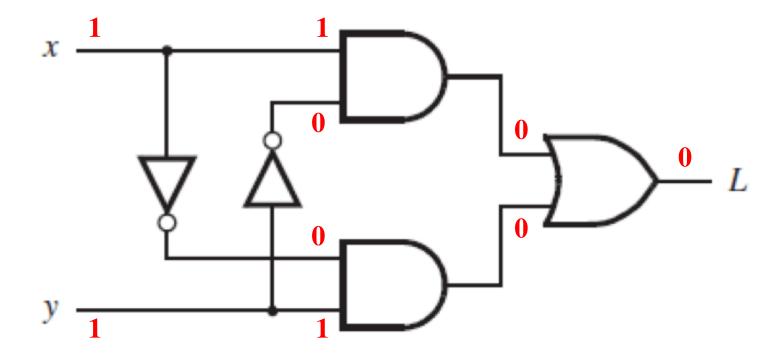

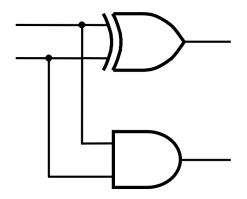

# **XOR Analysis**

# **XOR Analysis**

# **XOR Analysis**

# **XOR Analysis**

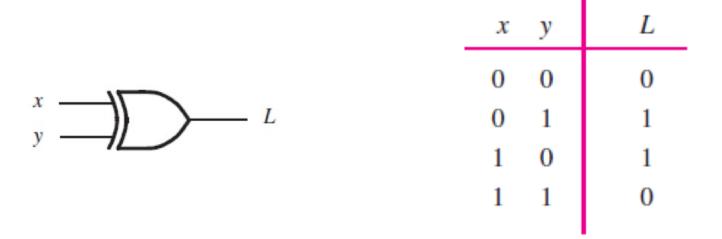

#### **Truth Table for XOR**

| х | у | L |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

|   |   |   |

#### **Truth Table for XOR**

The output is 1 only if the two inputs are different.

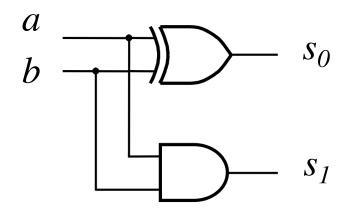

| a b | $s_1  s_0$ |

|-----|------------|

| 0 0 | 0 0        |

| 0 1 | 0 1        |

| 1 0 | 0 1        |

| 1 1 | 1 0        |

| a          | 0   | 0   | 1   | 1   |

|------------|-----|-----|-----|-----|

| + <i>b</i> | + 0 | + 1 | + 0 | + 1 |

| $s_1 s_0$  |     |     | 0 1 | 1 0 |

| a b | <i>s</i> <sub>1</sub> | $s_0$ |

|-----|-----------------------|-------|

| 0 0 | 0                     | 0     |

| 0 1 | 0                     | 1     |

| 1 0 | 0                     | 1     |

| 1 1 | 1                     | 0     |

| a          | 0   | 0   | 1   | 1   |

|------------|-----|-----|-----|-----|

| + <i>b</i> | + 0 | + 1 | + 0 | + 1 |

| $s_1 s_0$  | 0 0 |     | 0 1 | 1 0 |

| а | b | <i>s</i> <sub>1</sub> | $s_0$ |

|---|---|-----------------------|-------|

| 0 | 0 | 0                     | 0     |

| 0 | 1 | 0                     | 1     |

| 1 | 0 | 0                     | 1     |

| 1 | 1 | 1                     | 0     |

$$a$$

$+b$

$s_1 s_0$

| a b | <b>s</b> 1 | s <sub>0</sub> |  |

|-----|------------|----------------|--|

| 0 0 | 0          | 0              |  |

| 0 1 | 0          | 1              |  |

| 1 0 | 0          | 1              |  |

| 1 1 | 1          | 0              |  |

| a          | 0   | 0   | 1   | 1   |

|------------|-----|-----|-----|-----|

| + <i>b</i> | + 0 | + 1 | + 0 | + 1 |

| $s_1 s_0$  | 0 0 | 0 1 | 0 1 | 1 0 |

| <i>s</i> <sub>1</sub> | $s_0$ |

|-----------------------|-------|

| 0                     | 0     |

| 0                     | 1     |

| 0                     | 1     |

| 1                     | 0     |

|                       | 0     |

| a          | 0   | 0   | 1   | 1   |

|------------|-----|-----|-----|-----|

| + <i>b</i> | + 0 | + 1 | + 0 | + 1 |

| $s_1 s_0$  | 0 0 | 0 1 | 0 1 | 1 0 |

| a | b | S | <sup>5</sup> 1 | $s_0$ |  |

|---|---|---|----------------|-------|--|

| 0 | 0 | ( | 0              | 0     |  |

| 0 | 1 | ( | 0              | 1     |  |

| 1 | 0 | ( | 0              | 1     |  |

| 1 | 1 | 8 | 1              | 0     |  |

| 1 | 0 |   |                | 1 0   |  |

$$a$$

$+b$

$s_1 s_0$

| a b | <b>s</b> 1 | s <sub>0</sub> |  |

|-----|------------|----------------|--|

| 0 0 | 0          | 0              |  |

| 0 1 | 0          | 1              |  |

| 1 0 | 0          | 1              |  |

| 1 1 | 1          | 0              |  |

$$a + b$$

$s_1 s_0$

| a | b | <i>s</i> <sub>1</sub> | $s_0$ |

|---|---|-----------------------|-------|

| 0 | 0 | 0                     | 0     |

| 0 | 1 | 0                     | 1     |

| 1 | 0 | 0                     | 1     |

| 1 | 1 | 1                     | 0     |

| a b | <i>s</i> <sub>1</sub> | $s_0$ |

|-----|-----------------------|-------|

| 0 0 | 0                     | 0     |

| 0 1 | 0                     | 1     |

| 1 0 | 0                     | 1     |

| 1 1 | 1                     | 0     |

$$a$$

$+b$

$s_1 s_0$

| a | b | <i>s</i> <sub>1</sub> | $s_0$ |

|---|---|-----------------------|-------|

| 0 | 0 | 0                     | 0     |

| 0 | 1 | 0                     | 1     |

| 1 | 0 | 0                     | 1     |

| 1 | 1 | 1                     | 0     |

$$a + b$$

$s_1 s_0$

| a l | , | S | 1 s <sub>0</sub> |  |

|-----|---|---|------------------|--|

| 0 ( | ) | 0 | 0                |  |

| 0 1 | l | 0 | 1                |  |

| 1 ( | ) | 0 | 1                |  |

| 1 1 | l | 1 | 0                |  |

$$a + b$$

$s_1 s_0$

| a | b | <i>s</i> <sub>1</sub> | $s_0$ |  |

|---|---|-----------------------|-------|--|

| 0 | 0 | 0                     | 0     |  |

| 0 | 1 | 0                     | 1     |  |

| 1 | 0 | 0                     | 1     |  |

| 1 | 1 | 1                     | 0     |  |

|   |   |                       |       |  |

$$a$$

$+b$

$s_1 s_0$

| a | b | <i>s</i> <sub>1</sub> | $s_0$ |

|---|---|-----------------------|-------|

| 0 | 0 | 0                     | 0     |

| 0 | 1 | 0                     | 1     |

| 1 | 0 | 0                     | 1     |

| 1 | 1 | 1                     | 0     |

| a b | $s_1$ | s <sub>0</sub> |

|-----|-------|----------------|

| 0 0 | 0     | 0              |

| 0 1 | 0     | 1              |

| 1 0 | 0     | 1              |

| 1 1 | 1     | 0              |

|   |   |   | ?     |       |

|---|---|---|-------|-------|

|   | a | b | $s_1$ | $s_0$ |

| Ī | 0 | 0 | 0     | 0     |

|   | 0 | 1 | 0     | 1     |

|   | 1 | 0 | 0     | 1     |

|   | 1 | 1 | 1     | 0     |

|   |   |   |       |       |

|   | AND |  |       |       |

|---|-----|--|-------|-------|

| a | b   |  | $s_1$ | $s_0$ |

| 0 | 0   |  | 0     | 0     |

| 0 | 1   |  | 0     | 1     |

| 1 | 0   |  | 0     | 1     |

| 1 | 1   |  | 1     | 0     |

|   |     |  |       |       |

| a b | $s_1$ | s <sub>0</sub> |

|-----|-------|----------------|

| 0 0 | 0     | 0              |

| 0 1 | 0     | 1              |

| 1 0 | 0     | 1              |

| 1 1 | 1     | 0              |

|   |   |                       | ?     |  |

|---|---|-----------------------|-------|--|

| a | b | <i>s</i> <sub>1</sub> | $s_0$ |  |

| 0 | 0 | 0                     | 0     |  |

| 0 | 1 | 0                     | 1     |  |

| 1 | 0 | 0                     | 1     |  |

| 1 | 1 | 1                     | 0     |  |

|   |   |                       |       |  |

|   |   |                       | XOI   | 2 |

|---|---|-----------------------|-------|---|

| a | b | <i>s</i> <sub>1</sub> | $s_0$ |   |

| 0 | 0 | 0                     | 0     |   |

| 0 | 1 | 0                     | 1     |   |

| 1 | 0 | 0                     | 1     |   |

| 1 | 1 | 1                     | 0     |   |

|   |   |                       |       |   |

| a l | ,   | <i>s</i> <sub>1</sub> | $s_0$ |

|-----|-----|-----------------------|-------|

| 0 ( | )   | 0                     | 0     |

| 0 1 |     | 0                     | 1     |

| 1 ( | )   | 0                     | 1     |

| 1 1 | l l | 1                     | 0     |

| a | b | S | s <sub>0</sub> |  |

|---|---|---|----------------|--|

| 0 | 0 | 0 | 0              |  |

| 0 | 1 | 0 | 1              |  |

| 1 | 0 | 0 | 1              |  |

| 1 | 1 | 1 | 0              |  |

|   |   |   |                |  |

| • |

|---|

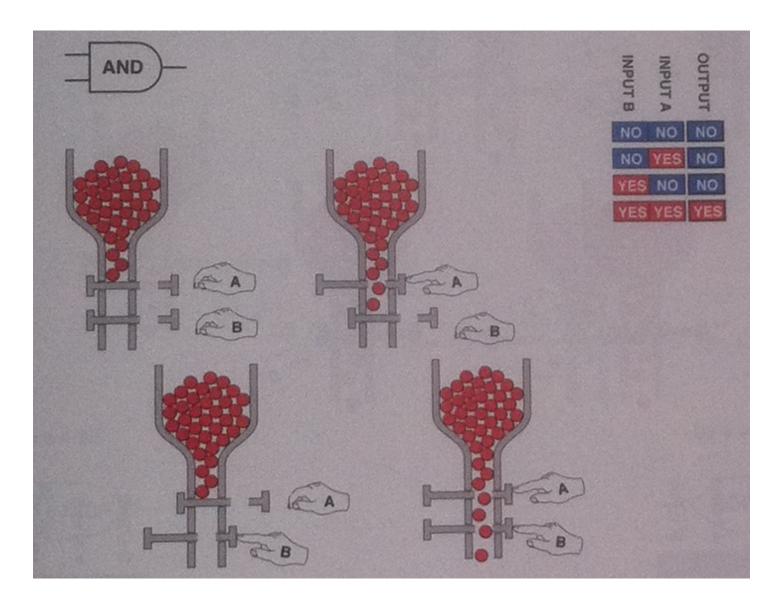

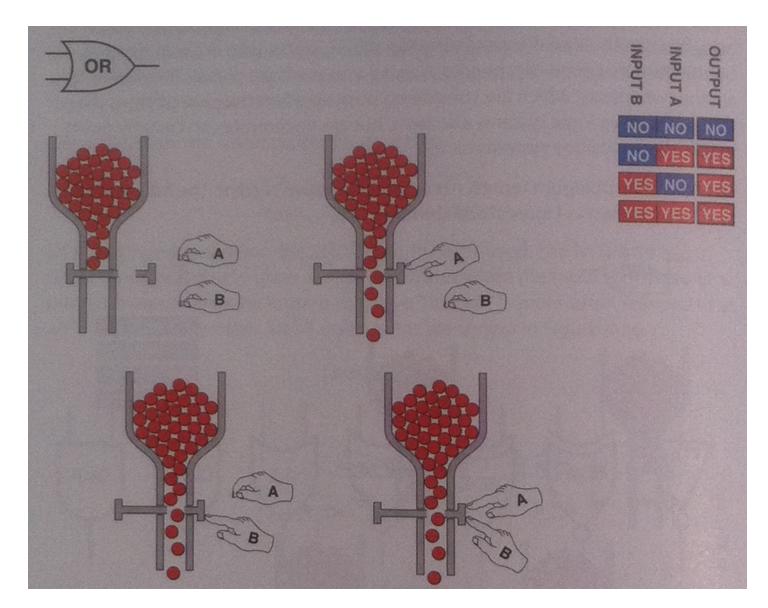

#### The following examples came from this book

[ Platt 2009 ]

[ Platt 2009 ]

**Questions?**