# **System-on-Chip Environment**

# SCE Version 2.2.0 Beta

# **Tutorial**

Samar Abdi Junyu Peng Haobo Yu Dongwan Shin Andreas Gerstlauer Rainer Doemer Daniel Gajski

Center for Embedded Computer Systems

University of California, Irvine

Irvine, CA 92697-3425

+1 (949) 824-8919

http://www.cecs.uci.edu

# System-on-Chip Environment: SCE Version 2.2.0 Beta; Tutorial

by Samar Abdi, Junyu Peng, Haobo Yu, Dongwan Shin, Andreas Gerstlauer, Rainer Doemer, and Daniel Gajski

Center for Embedded Computer Systems University of California, Irvine Irvine, CA 92697-3425 +1 (949) 824-8919 http://www.cecs.uci.edu Published July 23, 2003 Copyright © 2003 by CECS, UC Irvine

# **Table of Contents**

| 1. Introduction                                   | 1   |

|---------------------------------------------------|-----|

| 1.1. Motivation                                   | 1   |

| 1.2. SCE Goals                                    | 2   |

| 1.3. Models for System Design                     | 2   |

| 1.4. System-on-Chip Environment                   | 4   |

| 1.5. Design Example: GSM Vocoder                  |     |

| 1.6. Organization of the Tutorial                 | 5   |

| 2. System Specification Analysis                  | 9   |

| 2.1. Overview                                     | 9   |

| 2.2. Specification Capture                        | 10  |

| 2.2.1. SCE window                                 | 11  |

| 2.2.2. Open project                               | 12  |

| 2.2.3. Open specification model                   | 17  |

| 2.2.4. Browse specification model                 | 23  |

| 2.2.5. View specification model source code       | 27  |

| 2.3. Simulation and Analysis                      | 29  |

| 2.3.1. Simulate specification model               | 30  |

| 2.3.2. Profile specification model                | 37  |

| 2.3.3. Analyze profiling results                  | 40  |

| 2.4. Summary                                      | 47  |

| 3. System Level Design                            | 49  |

| 3.1. Overview                                     | 49  |

| 3.2. Architecture Exploration                     | 51  |

| 3.2.1. Try pure software implementation           | 52  |

| 3.2.2. Estimate performance                       | 65  |

| 3.2.3. Try software/hardware implementation       | 71  |

| 3.2.4. Estimate performance                       | 79  |

| 3.2.5. Generate architecture model                | 84  |

| 3.2.6. Browse architecture model                  | 87  |

| 3.2.7. Simulate architecture model (optional)     | 92  |

| 3.3. Software Scheduling and RTOS Model Insertion | 95  |

| 3.3.1. Serialize behaviors                        |     |

| 3.3.2. Generate serialized model                  | 105 |

| 3.3.3. Simulate serialized model (optional)       | 109 |

| 3.4. Communication Synthesis                      | 112 |

| 3.4.1. Select bus protocols                       | 113 |

| 3.4.2. Map channels to buses                      | 118 |

| 3.4.3. Generate communication model               | 120 |

| 3.4.4. Browse communication model              | 124 |

|------------------------------------------------|-----|

| 3.4.5. Simulate communication model (optional) | 128 |

| 3.5. Summary                                   | 131 |

| 4. Custom Hardware Design                      | 133 |

| 4.1. Overview                                  | 133 |

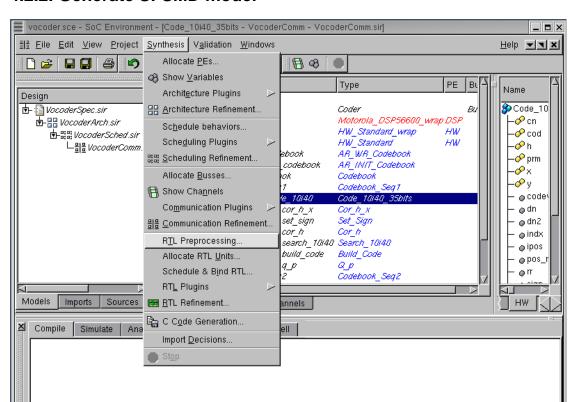

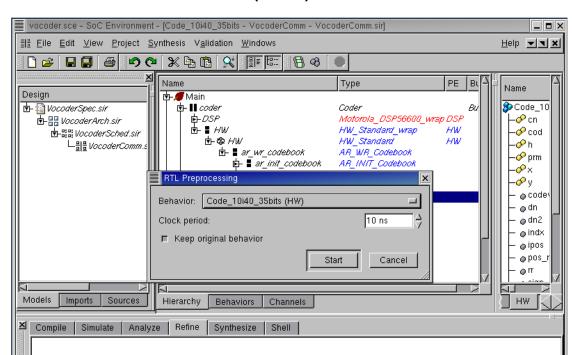

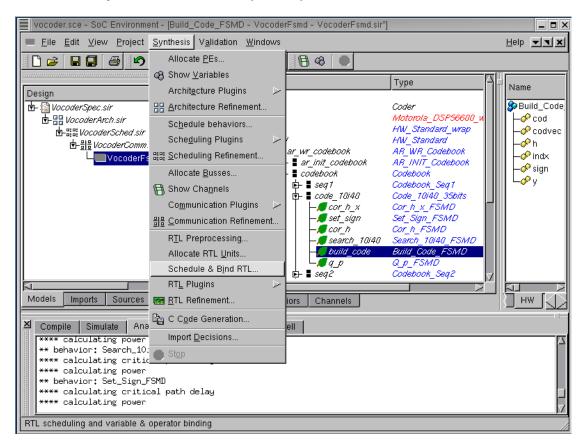

| 4.2. RTL Preprocessing                         | 135 |

| 4.2.1. View behavioral input model             | 136 |

| 4.2.2. Generate SFSMD model                    | 139 |

| 4.2.3. Browse SFSMD model                      |     |

| 4.2.4. View SFSMD model (optional)             | 144 |

| 4.2.5. Simulate SFSMD model (optional)         | 147 |

| 4.2.6. Analyze SFSMD model                     | 150 |

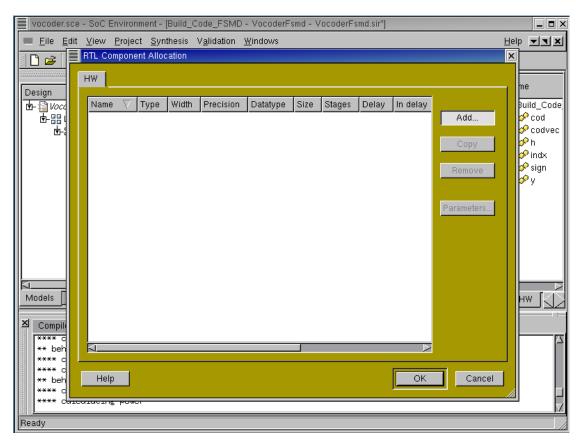

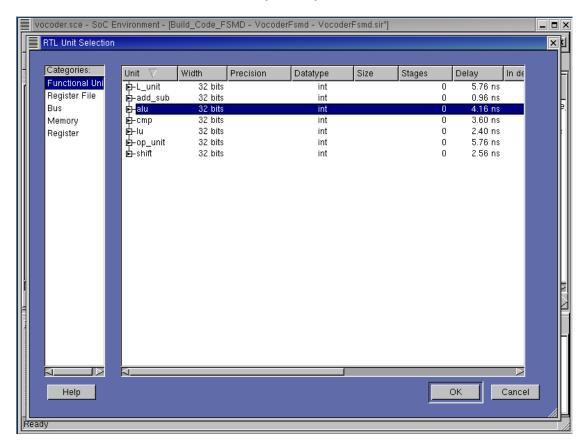

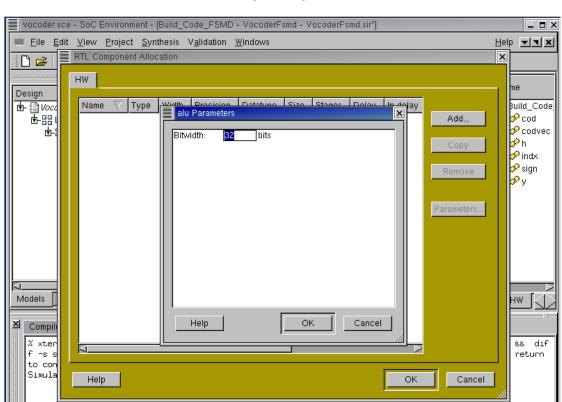

| 4.3. RTL Allocation                            | 157 |

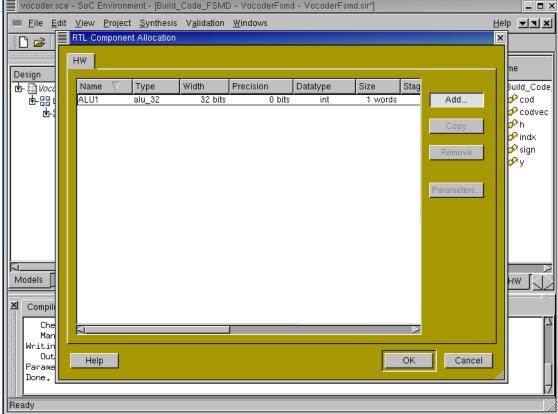

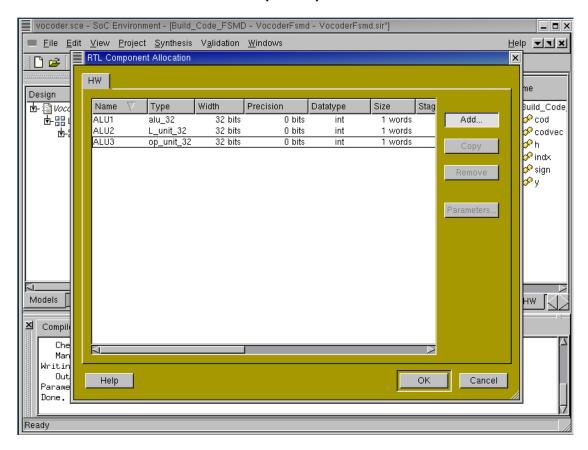

| 4.3.1. Allocate functional units               | 158 |

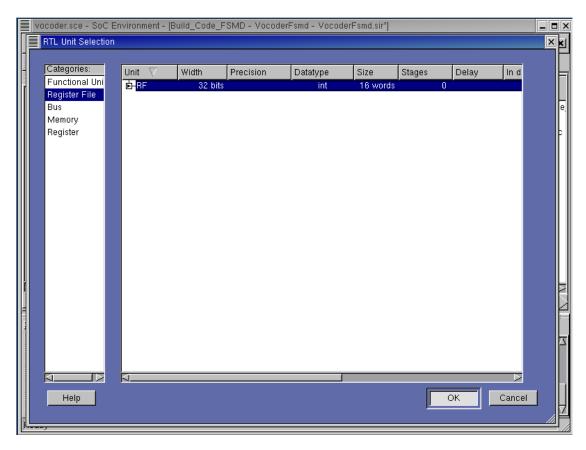

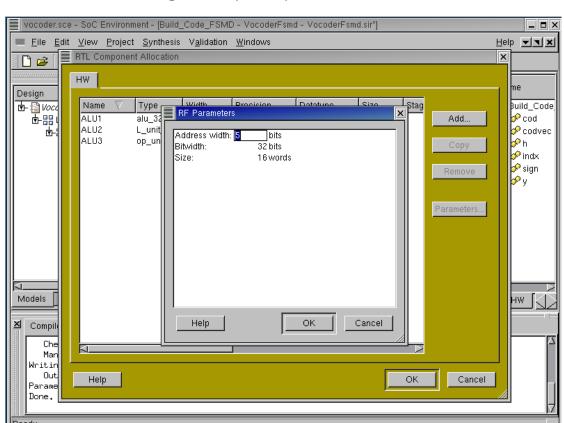

| 4.3.2. Allocate storage units                  |     |

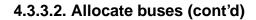

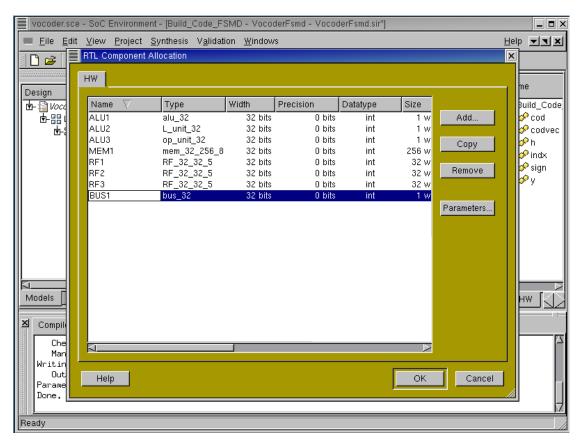

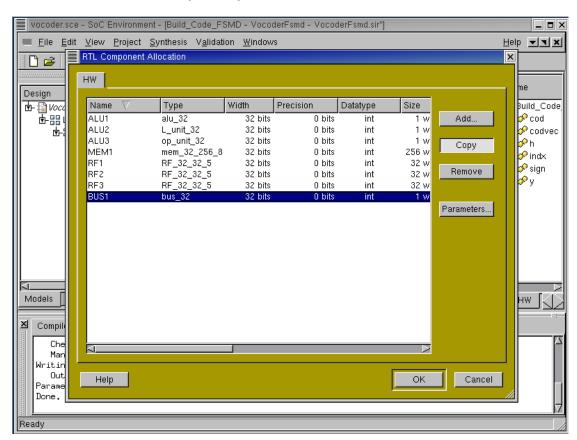

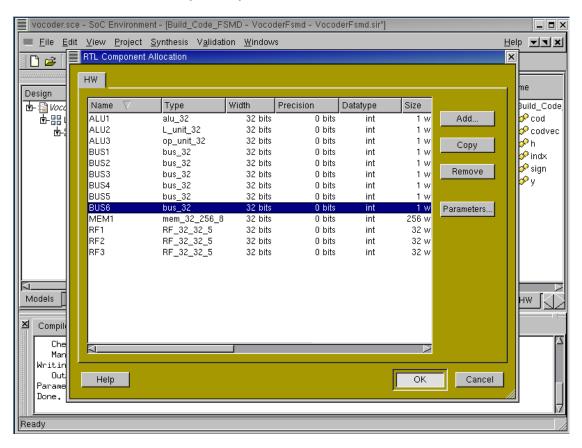

| 4.3.3. Allocate buses                          | 170 |

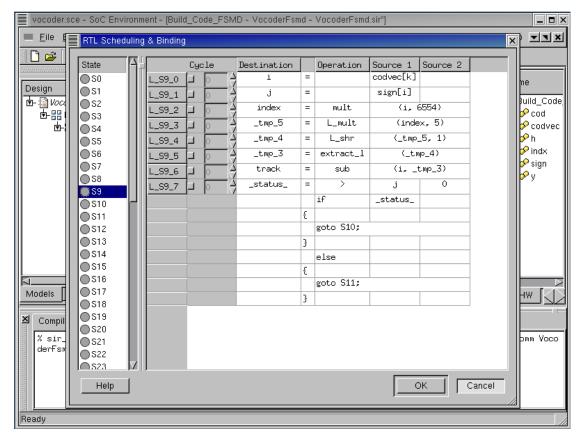

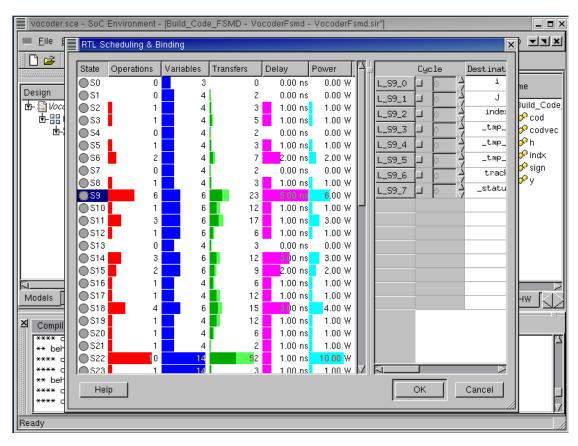

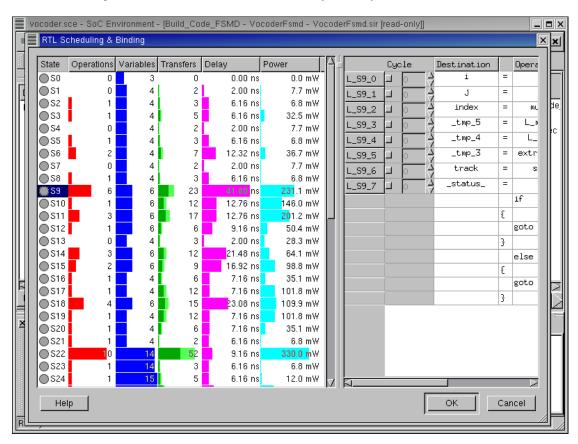

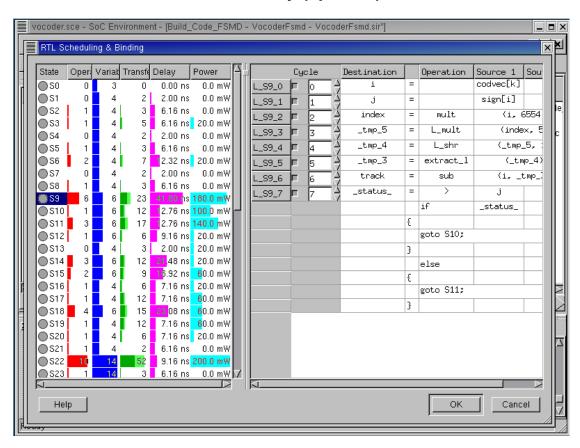

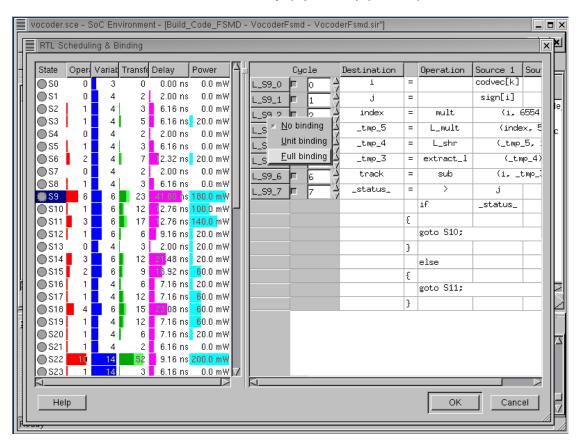

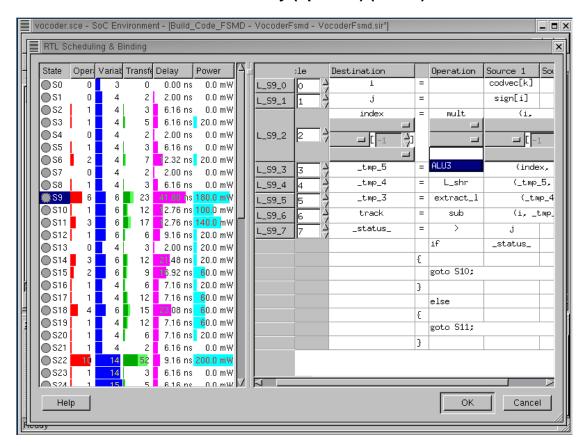

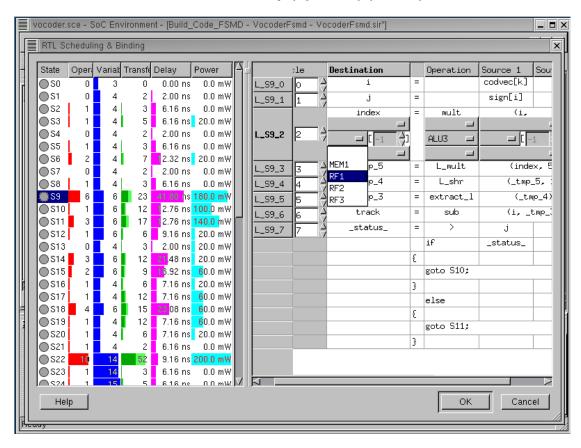

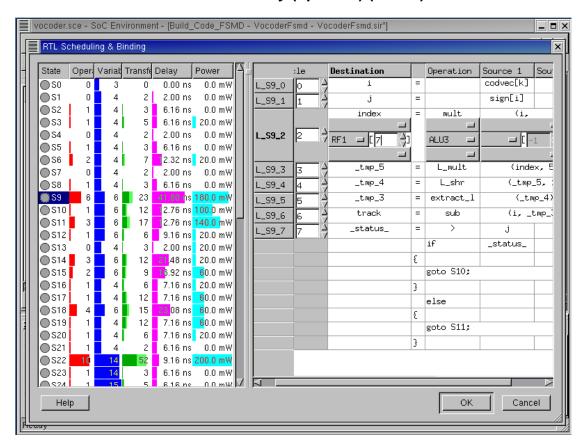

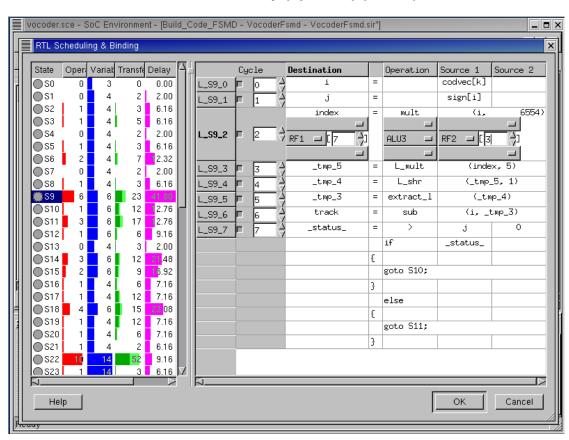

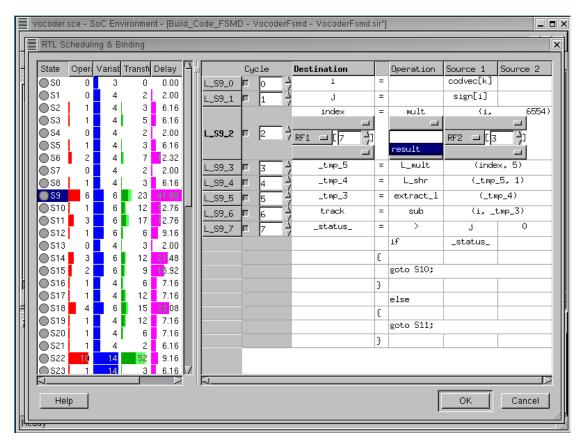

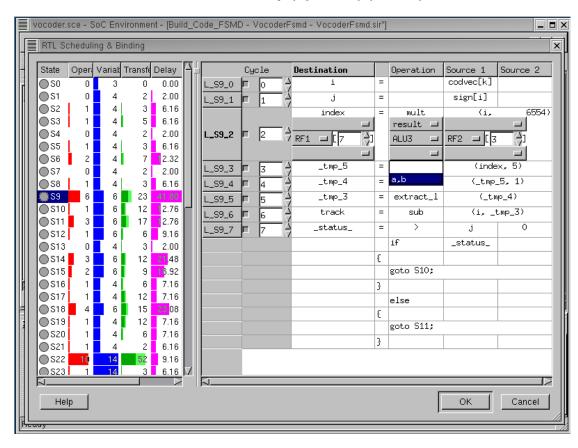

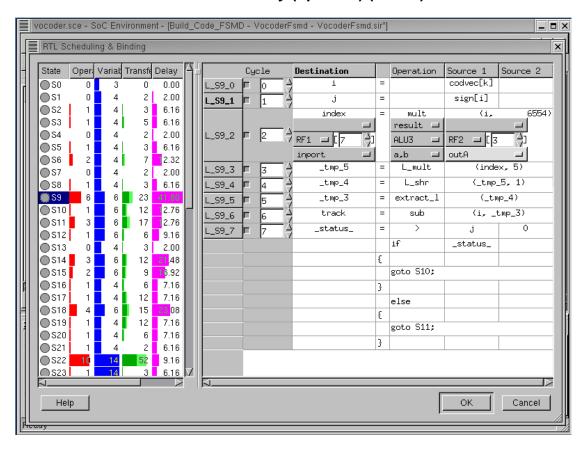

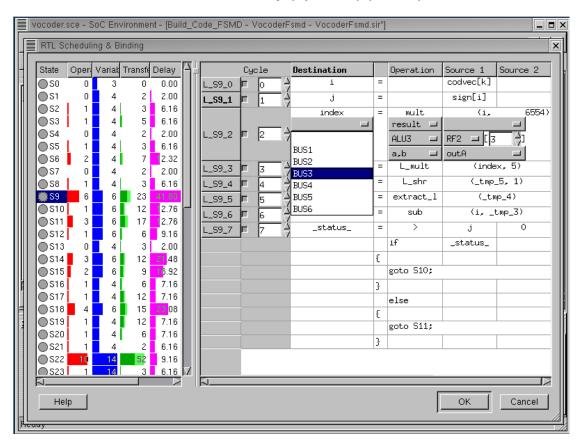

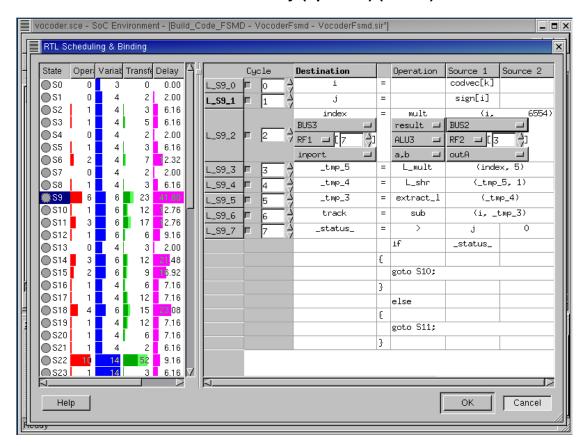

| 4.4. RTL Scheduling and Binding                | 179 |

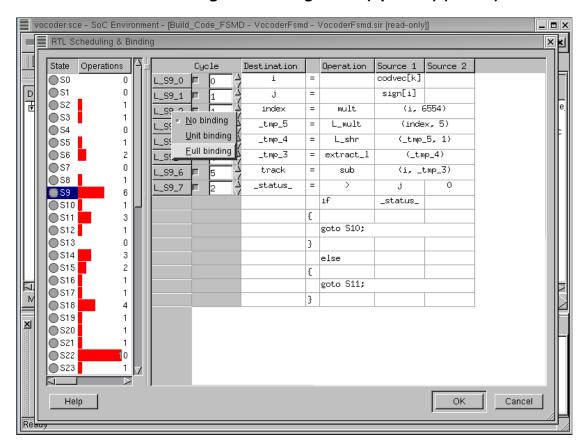

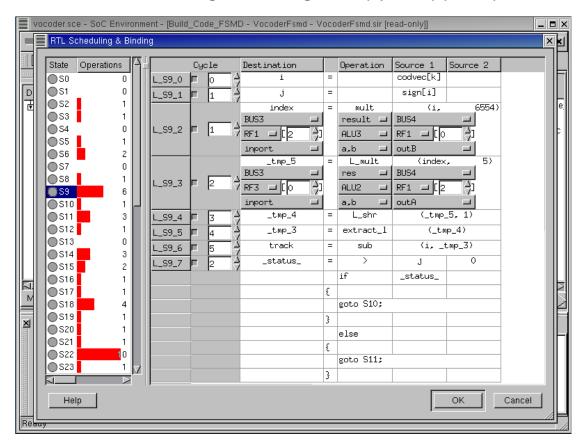

| 4.4.1. Schedule and bind manually (optional)   | 180 |

| 4.4.2. Schedule and bind automatically         |     |

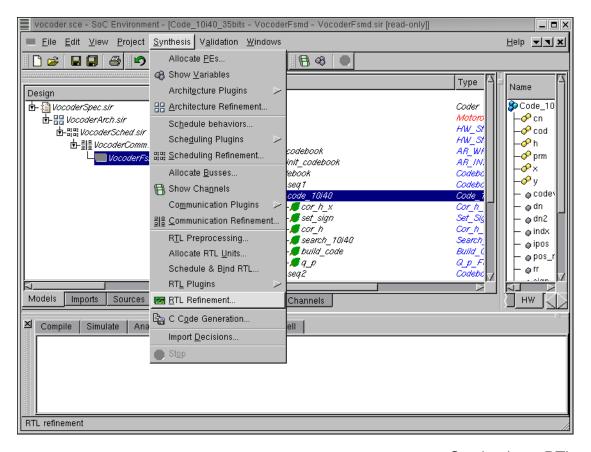

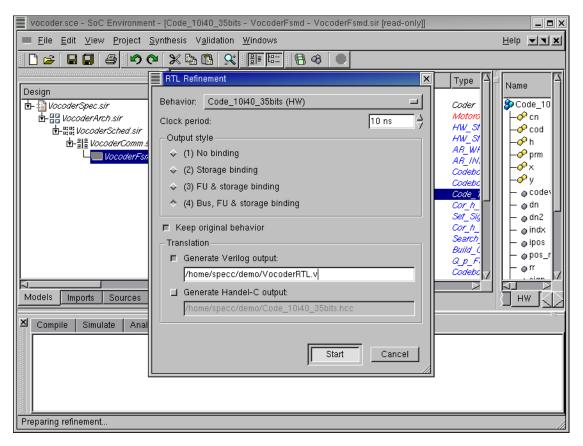

| 4.5. RTL Refinement                            | 198 |

| 4.5.1. Generate RTL model                      | 199 |

| 4.5.2. Browse RTL model                        | 204 |

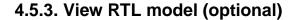

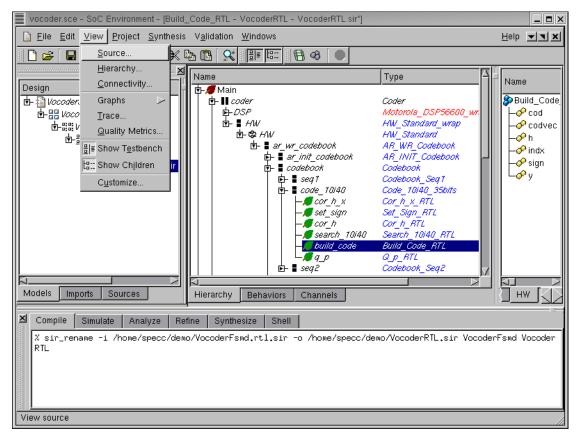

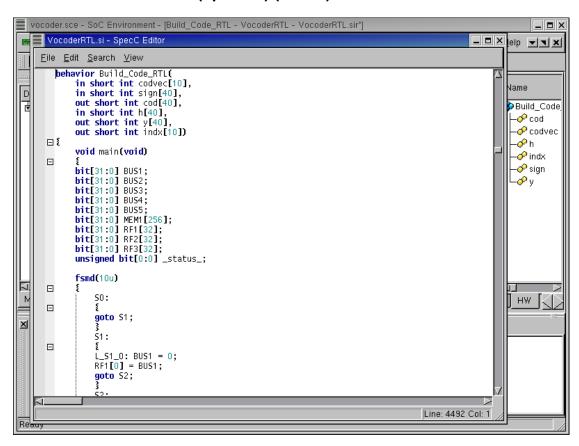

| 4.5.3. View RTL model (optional)               | 206 |

| 4.5.4. View Verilog RTL model (optional)       |     |

| 4.5.5. Simulate RTL model (optional)           | 211 |

| 4.6. Summary                                   | 214 |

| 5. Embedded Software Design                    | 215 |

| 5.1. Overview                                  |     |

| 5.2. SW code generation                        | 216 |

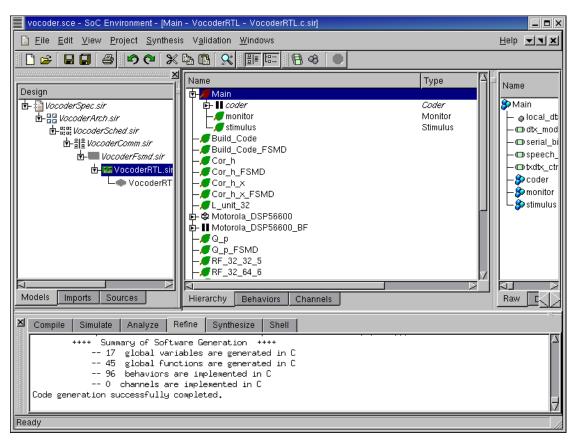

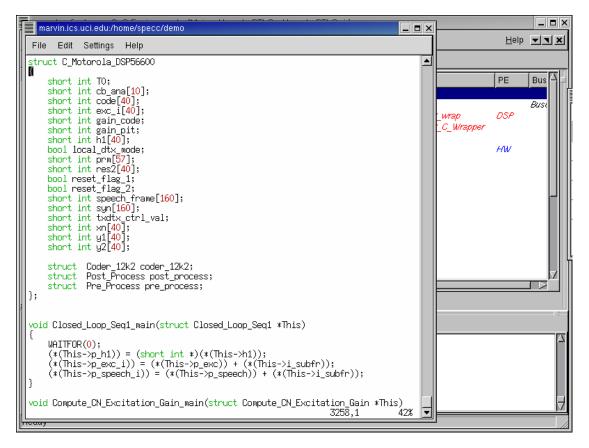

| 5.2.1. Generate C code                         | 217 |

| 5.2.2. Browse and View C code                  | 221 |

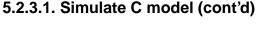

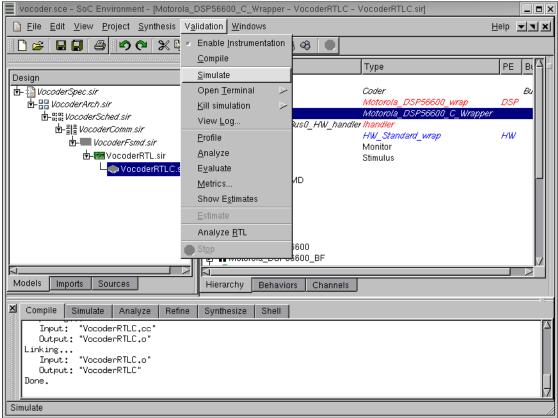

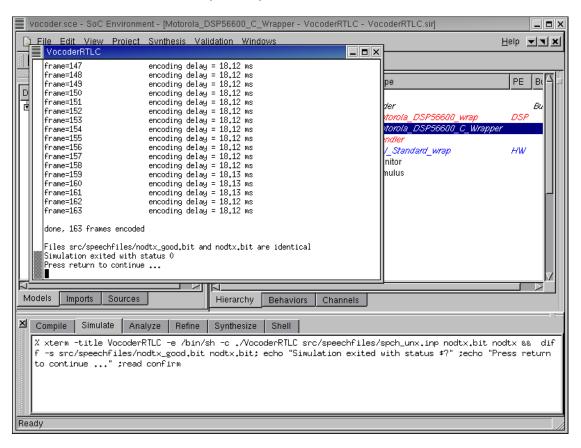

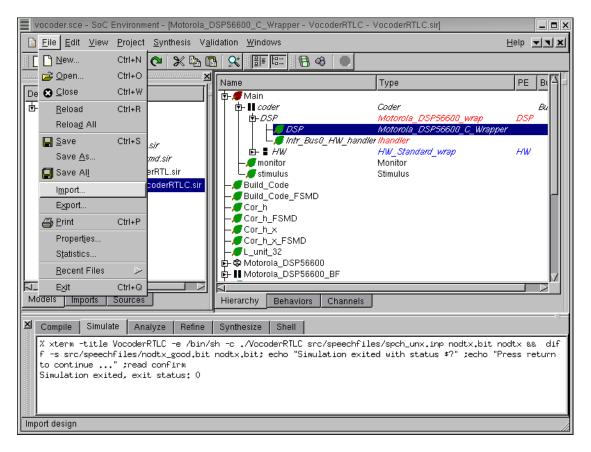

| 5.2.3. Simulate C model (optional)             | 222 |

| 5.3. Instruction set simulation                | 225 |

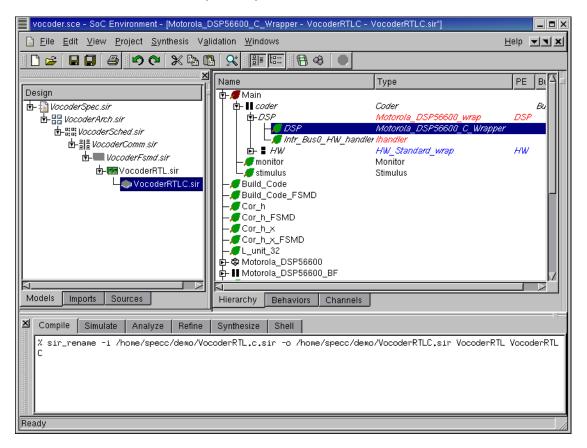

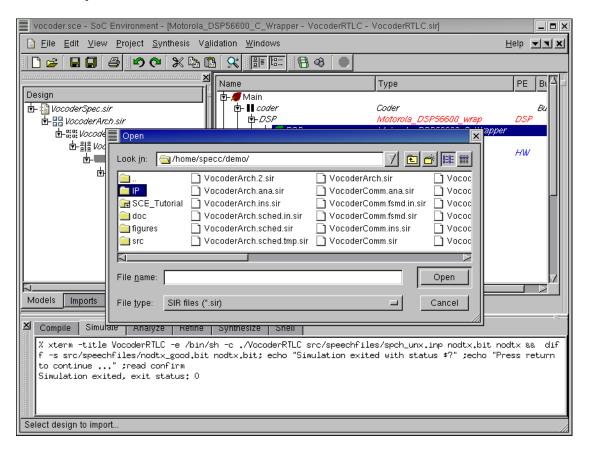

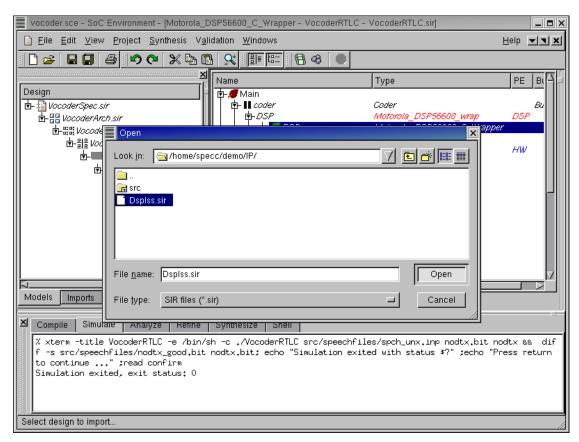

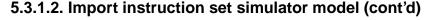

| 5.3.1. Import instruction set simulator model  | 226 |

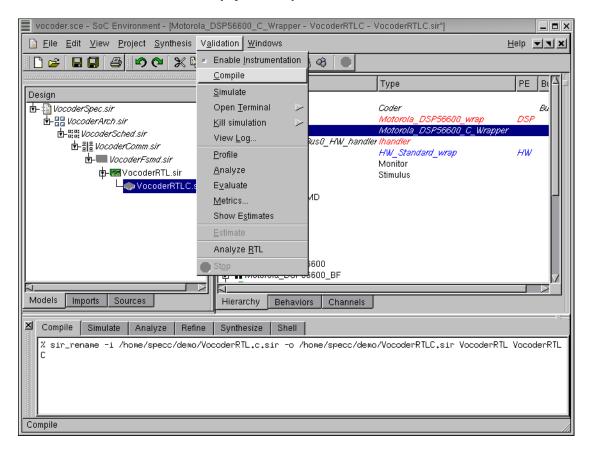

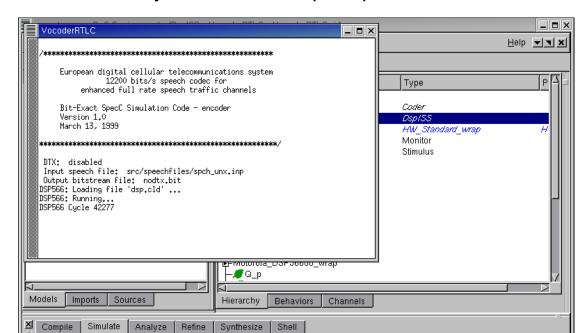

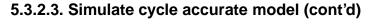

| 5.3.2. Simulate cycle accurate model           | 231 |

| 5.4. Summary                                   | 236 |

| 6. Conclusion                                  | 237 |

| A. Frequently Asked Questions                  | 239 |

| References                                     | 245 |

# **Chapter 1. Introduction**

The basic purpose of this tutorial is to guide a user through our System-on-Chip design environment (SCE). SCE helps designers to take an abstract functional description of the design and produce an implementation. We begin with a brief overview of our SoC methodology by describing the design flow and various abstraction levels. The overview also covers the user interfaces and the tools that support the design flow.

We then describe the example that we use throughout this tutorial. We selected the GSM Vocoder as an example for a variety of reasons. For one, the Vocoder is a fairly large design and is an apt representative of a typical component of a System-on-Chip design. Moreover, the functional specification of the Vocoder is well defined and publicly available from the European Telecommunication Standards Institute (ETSI).

The tutorial gives a step by step illustration of using the System-on-Chip Environment. Screenshots of the GUI are presented to aid the user in using the various features of SCE. (Please note that, depending on your specific version of the System-on-Chip Environment SCE and your system settings, the screen shots shown in this document may be slightly different from the actual display on your screen.) Over the course of this chapter, the user is guided on synthesizing the Vocoder model from an abstract specification to a clock cycle accurate implementation. The screenshots at each design step are supplemented with brief observations and the rationale for making design decisions. This would help the designer to gain an insight into the design process instead of merely following the steps. We wind up the tutorial with a conclusion and references. This tutorial assumes that the readers of this tutorial have basic knowledge of system design tasks and flow. In case the reader feels difficulty going following this tutorial, he can always go to the Appendix A: FAQ (Frequently Asked Questions) at the end of the tutorial to seek more explanation.

#### 1.1. Motivation

System-on-Chip capability introduces new challenges in the design process. For one, co-design becomes a crucial issue. Software and Hardware must be developed together. However, both Software and Hardware designers have different views of the system and they use different design and modeling techniques.

Secondly, the process of system design from specification to mask is long and elaborate. The process must therefore be split into several steps. At each design step, models must be written and relevant properties must be verified.

Thirdly, the system designers are not particularly fond of having to learn different languages. Moreover, writing different models and validating them for each step in the design process is a huge overkill. Designers prefer to create solutions rather than write several models to verify their designs.

It is with these aspects and challenges in mind that we have come up with a Systemon-Chip Environment that takes off the drudgery of manual repetitive work from the designers by generating each successive model automatically according to the decisions made by the designers.

#### 1.2. SCE Goals

SCE represents a new technology that allows designers to capture system specification as a composition of C-functions. These are automatically refined into different models required at each step of the design process. Therefore designers can devote more effort to the creative part of designing and the tools can create models for validation and synthesis. The end result is that the designers do not need to learn new system level design languages (SystemC, SpecC, Superlog, etc.) or even the existing Hardware Description Languages (Verilog, VHDL).

Consequently, the designers have to enter only the golden specification of the design and make design decisions interactively in SCE. The models for simulation, synthesis and verification are generated automatically.

# 1.3. Models for System Design

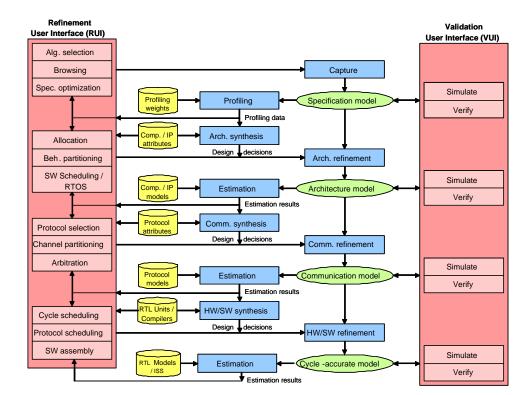

Figure 1-1. System-on-Chip Environment

The System-on-Chip design environment is shown in figure 1-1. It consists of 4 levels of model abstraction, namely specification, architecture, communication and cycle-accurate models. Consequently, there are 3 refinement steps, namely architecture refinement, communication refinement and HW/SW refinement. These refinement steps are preformed in the top-down order as shown. As shown in figure 1-1, we begin with an abstract specification model. The specification model is untimed and has only the functional description of the design. Architecture refinement transforms this specification to an architecture model. It involves partitioning the design and mapping the partitions onto the selected components. The architecture model thus reflects the intended architecture for the design. The next step, communication refinement, adds system busses to the design and maps the abstract communication between components onto the busses. The resulted design is a timing accurate communication model (bus functional model). The final step is HW/SW refinement which produces clock cycle accurate RTL model for

the hardware components and instruction set specific assembly code for the processors. All models have well defined semantics, are executable and can be validated through simulation.

# 1.4. System-on-Chip Environment

The SCE provides an environment for modeling, synthesis and validation. It includes a graphical user interface (GUI) and a set of tools to facilitate the design flow and perform the aforementioned refinement steps. The two major components of the GUI are the Refinement User Interface (RUI) on the left and the Validation User Interface (VUI) on the right as shown in figure 1-1. The RUI allows designers to make and input design decisions, such as component allocation, specification mapping. With design decisions made, refinement tools can be invoked inside RUI to refine models. The VUI allows the simulation of all models to validate the design at each stage of the design flow.

Each of the boxes corresponds to a tool which performs a specific task automatically. A profiling tool is used to obtain the characteristics of the initial specification, which serves as the basis for architecture exploration. The refinement tool set automatically transforms models based on relevant design decisions. The estimation tool set produces quality metrics for each intermediate models, which can be evaluated by designers.

With the assistance of the GUI and tool set, it is relatively easy for designer to step through the design process. With the editing, browsing and algorithm selection capability provided by RUI, a specification model can be efficiently captured by designers. Based on the information profiled on the specification, designers input architectural decisions and apply the architecture refinement tool to derive the architecture model. If the estimated metrics are satisfactory, designers can focus on communication issues, such as protocol selection and channel partitioning. With communication decisions made, the communication refinement tool is used to generate the communication model. Finally, the implementation model is produced in the similar fashion. The implementation model is ready for RTL synthesis.

We are currently in the process of developing tools for automating the synthesis tasks for system level design shown in the exploration engine. The tutorial presents automatic RTL synthesis. The next challenge is to automatically perform architecture and communication synthesis.

# 1.5. Design Example: GSM Vocoder

Long-Term

Pitch Filter

Delay / Adaptive codebook

Residual

Pulses

Fixed codebook

Long-Term

Short-term

Synthesis Filter

10th-order LP filter

Figure 1-2. GSM Vocoder

The example design used throughout this tutorial is the GSM Vocoder system, which is employed worldwide for cellular phone networks. Figure 1-2 shows the GSM Vocoder speech synthesis model. A sequence of pulses is combined with the output of a long term pitch filter. Together they model the buzz produced by the glottis and they build the excitation for the final speech synthesis filter, which in turn models the throat and the mouth as a system of lossless tubes.

The example used in this tutorial encodes speech data comprised of frames. Each frame in turn comprises of 4 sub-frames. Overall, each sub-frame has 40 samples which translate to 5 ms of speech. Thus each frame has 20 ms of speech and 160 samples. Each frame uses 244 bits. The transcoding constraint (ie. back to back encoder/decoder) is less than 10 ms for the first sub-frame and less than 20 ms for the whole frame (consisting of 4 sub-frames).

The vocoder standard, published by the European Telecommunication Standards Institute (ETSI), contains a bit-exact reference implementation of the standard in ANSI C. This reference code was taken as the the basis for developing the specification model. At the lowest level, the algorithms in C could be directly reused in the leaf behaviors without modification. Then the C function hierarchy was converted into a clean and efficient hierarchical specification by analyzing dependencies, exposing available parallelism, etc. The final specification model is composed of 9139 lines of SpecC code, which contains 73 leaf behaviors.

### 1.6. Organization of the Tutorial

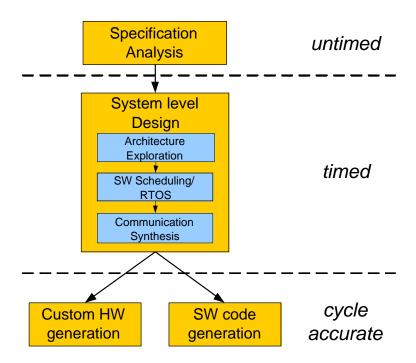

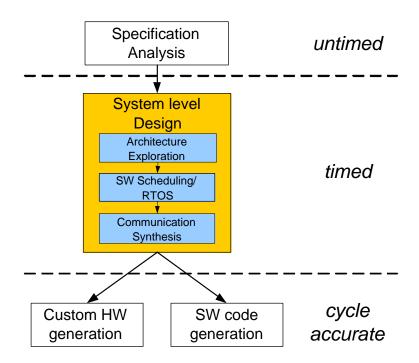

Figure 1-3. Task flow for system design with SCE

The tasks in system design with SCE are organized as shown in figure 1-3. Each of the tasks is explained in a separate chapter in this tutorial. We will start with a specification model and show how to get started with SCE. At this level, we will be working with untimed functional models. Following that, we will look at system level exploration and refinements, where the involved models will have a quantitative notion of time. Once we get a system model with well defined HW and SW components and the interfaces between them, we will proceed to generate custom hardware and processor specific software. These final steps will produce cycle accurate models.

Each design task is composed of several steps like model analysis, browsing, generation of new models and simulation. Not all these steps are crucial for the demo to proceed smoothly. Some steps are marked as optional and may be avoided during the course of this tutorial. If the designer is sufficiently comfortable with the tool's result, he or she can avoid the typically optional steps of simulation and code viewing.

If the designer is booting from the CD-ROM, the setup is already prepared. Otherwise, the designer may follow the following steps to set up the demo. Start

with a new shell of your choice. If you are working with a c-shell, run "source \$SCE\_INSTALLATION\_PATH/bin/setup.csh". If you are working with bourne shell, run "\$SCE\_INSTALLATION\_PATH/bin/setup.sh". Now run "setup\_demo" to setup the demonstration in the current directory. This will add some new files to be used during the demo.

#### **Acknowledgment:**

The authors would like to thank Tsuneo Kinoshita of NASDA, Japan for his patience in going through the tutorial and helping us make it more understandable and comprehensive. We would also like to thank Yoshihisa Kojima of the University of Tokyo for his help in uncovering several mistakes in the tutorial's text.

# Chapter 1. Introduction

# **Chapter 2. System Specification Analysis**

#### 2.1. Overview

Specification untimed **Analysis** System level Design Architecture Exploration timed SW Scheduling/ **RTOS** Communication Synthesis cycle Custom HW SW code generation generation accurate

Figure 2-1. Specification analysis using SCE

The system design process starts with the specification model written by the user to specify the desired system functionality. It forms the input to the series of exploration and refinement steps in the SoC design methodology. Moreover, the specification model defines the granularity for exploration through the size of the leaf behaviors. It exposes all available parallelism and uses hierarchy to group related functionality and manage complexity.

In this chapter, we go through the steps of creating a project in SCE and initiating the system design process as highlighted in figure 2-1. The various aspects of the specification are observed through simulation and profiling. Also, the model is graphically viewed with the help of SCE tools.

# 2.2. Specification Capture

The system design process starts with the specification model written by the user to specify the desired system functionality. It forms the input to the series of exploration and refinement steps in the SoC design methodology. Moreover, the specification model defines the granularity for exploration through the size of the leaf behaviors. It exposes all available parallelism and uses hierarchy to group related functionality and manage complexity.

In this section, we go through the steps of creating a project in SCE and initiating the system design process. The various aspects of the specification are observed through simulation and profiling. Also, the model is graphically viewed with the help of SCE tools.

The models that we will deal with in this phase of system design are untimed functional models. The tasks of the system specification, referred to as behaviors in our parlance, follow a causal order of execution. The main idea in this section is to introduce the user to the SCE GUI and to demonstrate the capability of graphically viewing the behaviors and their organization in the specification model.

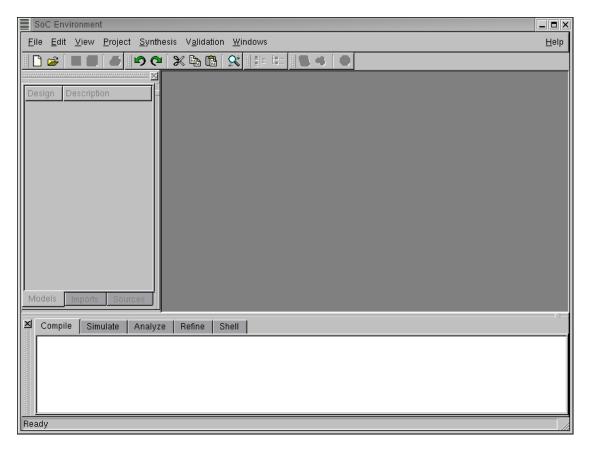

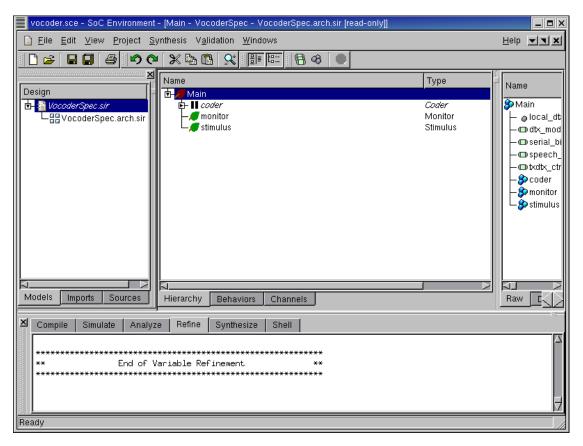

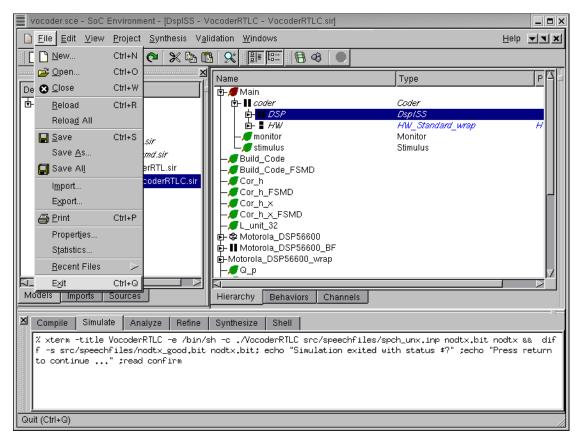

#### 2.2.1. SCE window

To launch the SCE GUI, simply run "sce" from the shell prompt. On launching the System-on-Chip Environment (SCE), we see the above GUI. The GUI is divided broadly into three parts. First is the "project management" window on the top left part of the GUI, which maintains the set of models in the open projects. This window becomes active once a project is opened and a design is added to it. Secondly, we have the "design management" window on the top right where the currently active design is maintained. It shows the hierarchy tree for the design and maintains various statistics associated with it. Finally, we have the "logging" window at the bottom of the GUI, which keeps the log of various tools that are run during the course of the demo. We keep logs of compilation, simulation, analysis and refinement of models.

The GUI also consists of a tool bar and shortcuts for menu items. The File menu handles file related services like opening designs, importing models etc. The Edit menu is for editing purposes. The View menu allows various methods of graphically viewing the design. The Project menu manages various projects. The Synthesis menu provides for launching the various refinement tools and making synthesis decisions. The Validation menu is primarily for compiling or simulating models.

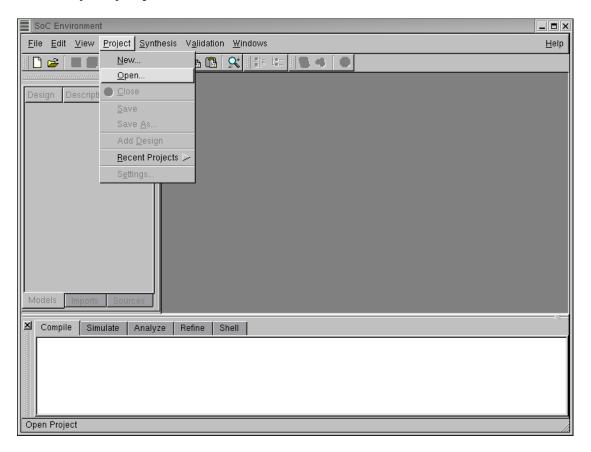

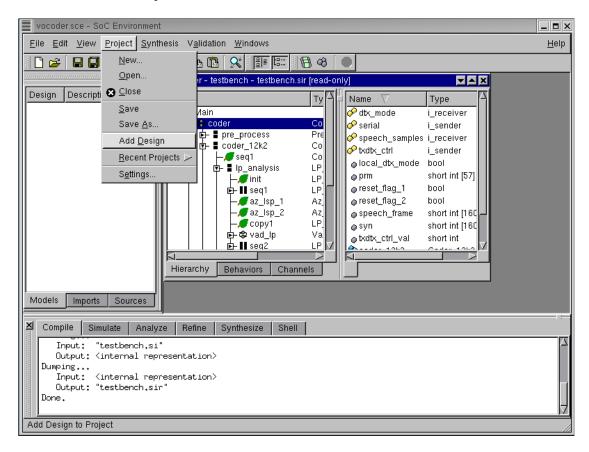

# 2.2.2. Open project

The first step in working with SCE is opening a project. A project is associated with every design process since each design might impose a different set of databases or dependencies. The project is hence used by the designer to customize the environment for a particular design process. We begin by selecting Project—Open from the menu bar.

### 2.2.2.1. Open project (cont'd)

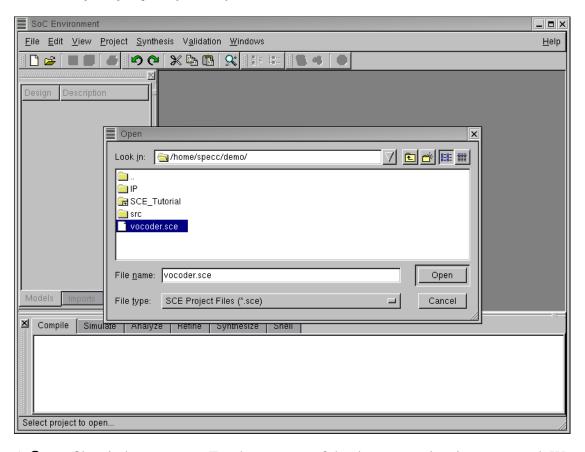

A Open file window pops up. For the purpose of the demo, a project is pre-created. We simply open it by selecting the project "vocoder.sce" and left click on Open button on the right corner of the the pop-up window.

# 2.2.2.2. Open project (cont'd)

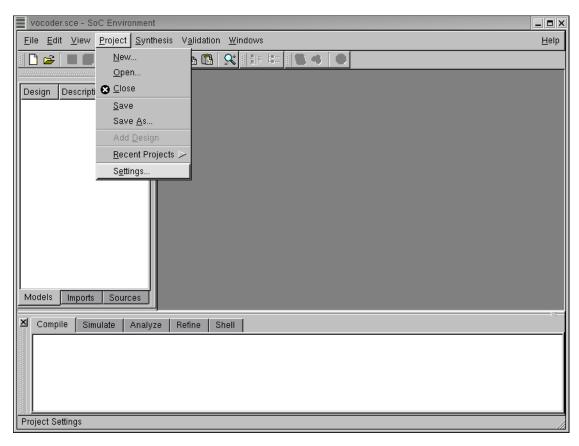

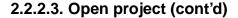

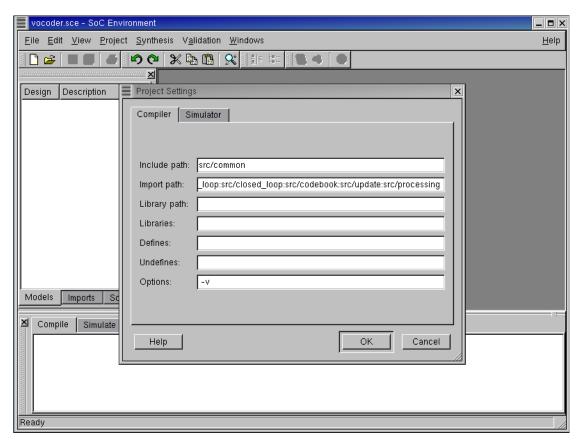

Since we need to ensure that the paths to dependencies are correctly set, we now check the settings for this precreated "vocoder.sce" project by selecting  $Project \longrightarrow Settings...$  from the top menu bar.

We now see the compiler settings showing the import path for the model's libraries and the '-v' (verbose) option. The Include path setting gives the path which is searched for header files. The Import path is searched for files imported into the model. The Library path is used for looking up the libraries used during compilation. There are also settings provided for specifying which libraries to link against, which macros to define and which to undefine. These settings basically form the compilation command. To check the simulator settings, left click on the Simulator tab.

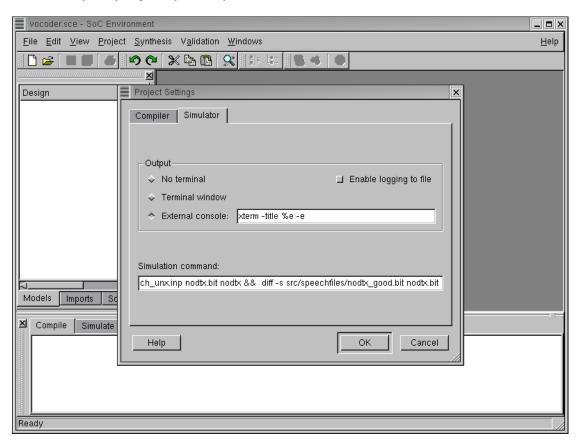

#### 2.2.2.4. Open project (cont'd)

We now see the simulator settings showing the simulation command for the "vocoder.sce" project. There are settings available to direct the output of the model simulation. As can be seen, the simulation output may be directed to a terminal, logged to a file or dumped to an external console. For the demo, we direct the output of the simulation to an xterm. Also note that the simulation command may be specified in the settings. This command is invoked when the model is validated after compilation. The vocoder simulation processes 163 frames of speech and the output is matched against a golden file. Press OK to proceed.

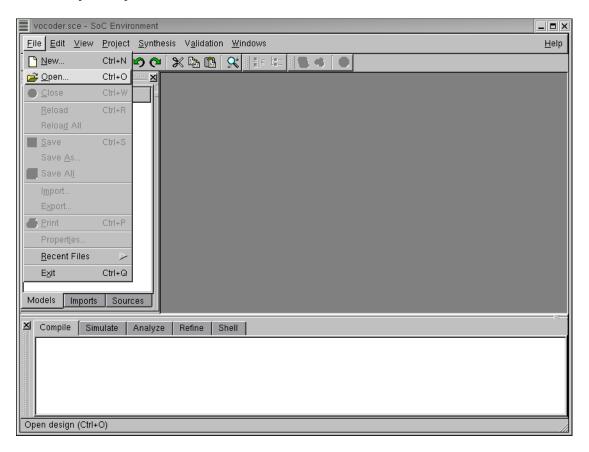

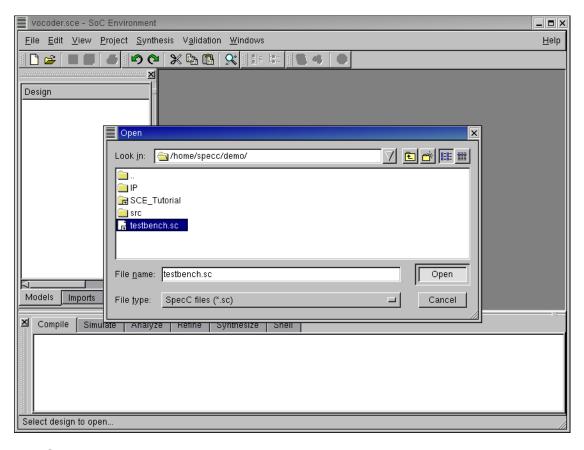

### 2.2.3. Open specification model

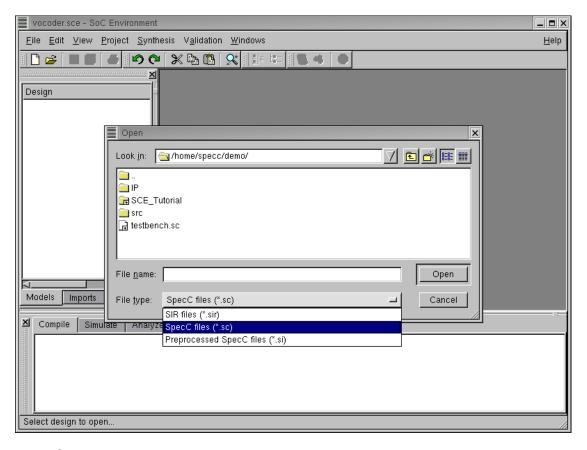

We start with the specification that was already captured as a model. We open this model to see if it meets the desired behavior. Once the model is validated to be "golden", we will start refining it and adding implementation details to it. We open the specification model for the Vocoder example by selecting File——Open from the menu bar.

A file Open window pops up showing the SpecC internal representation (SIR) files. The internal representation files are a collection of data structures used by the tools in the environment. They uniquely identify a SpecC model. At this time however, the design is available only in its source form. We therefore need to start with the sources. Select "SpecC files (\*.sc)" to view the source files.

The Open is updated to show the available source files of the GSM Vocoder design specification. Select the file containing the top hierarchy of the model. In this case, the file is "testbench.sc". The testbench instantiates the design-under-test (DUT) and the corresponding modules for triggering the test vectors and for observing the outputs. To open this file Left click on Open.

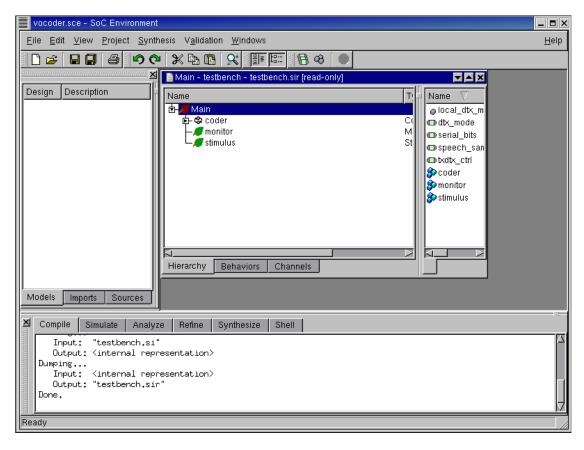

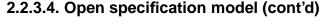

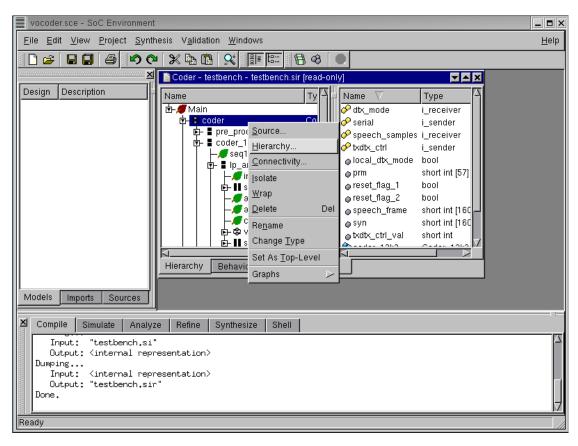

Note that a new window pops up in the design management area. It has two sub-windows. The sub-window on the left shows the Vocoder design hierarchy. The leaf behaviors are shown with a leaf icon next to them. For instance, we see two leaf behaviors: "stimulus", which is used to feed the test vectors to the design, and "monitor", which validates the response. "coder" is the top behavior of the Vocoder model. It can be seen from the icon besides the "coder" behavior that it is an FSM composition. This means the Vocoder specification is captured as a finite state machine. Also note in the logging window that the SoC design has been compiled into an intermediate format. Upon opening a source file into the design window, it is automatically compiled into its unique internal representation files (SIR) which in turn is used by the tools that work on the model.

The model may be browsed using the design hierarchy window. Parallel composition is shown with || shaped icons and sequential composition with ':' shaped icons. On selecting a behavior in the design hierarchy window, we can see the behavior's characteristics in the right sub-window. For instance, the behavior "vad\_lp" has ports shown with yellow icons, variables with gray icons and sub-behaviors with blue icons.

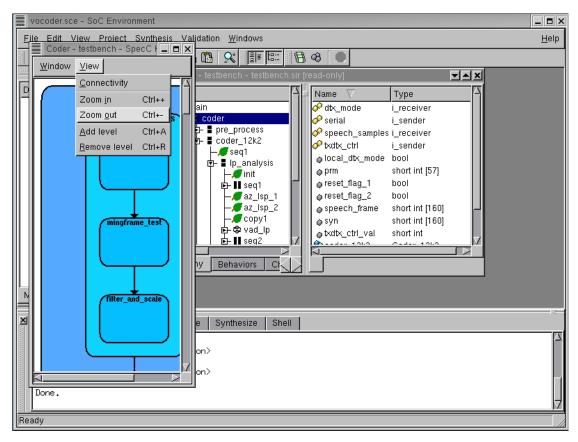

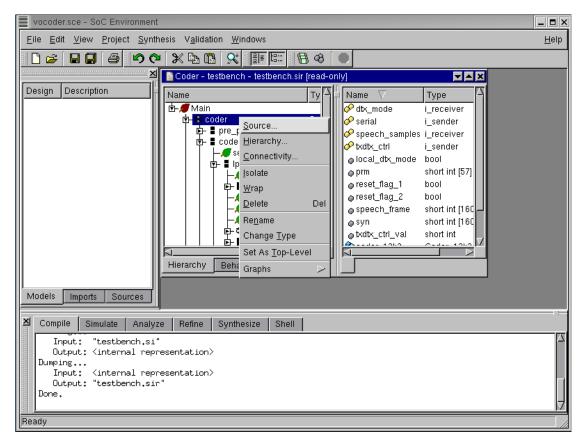

Before making any synthesis decisions, it is important to understand the composition of the specification model. It is useful because the composition really tells us which features of the model may be exploited to gain maximum productivity. Naturally, the most intuitive way to understand a model's structure is through a graphical representation. Since system models are typically very complex, it is more convenient to have a hierarchical view which may be easily traversed. SCE provides for such a mechanism. To graphically view the hierarchy, from the design hierarchy window, select "coder". Right click and select Hierarchy. Notice that the menu provides for a variety of services on individual behaviors. We shall be using one or more of these in due course.

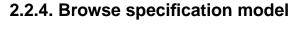

A new window pops up showing the Vocoder model in graphical form. As noted earlier, the specification is an FSM at the top level with three states of pre-processing, the bulk of the coder functionality itself and finally post-processing.

### 2.2.4.1. Browse specification model (cont'd)

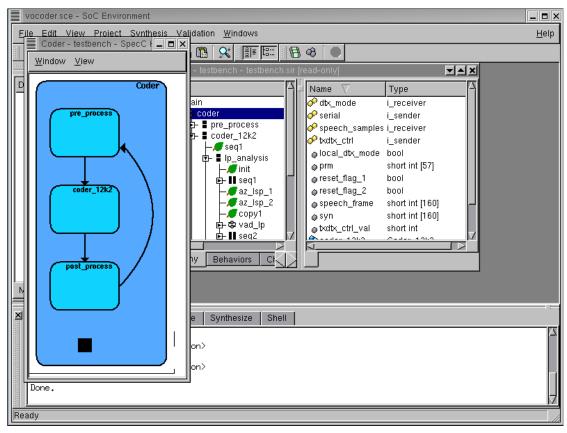

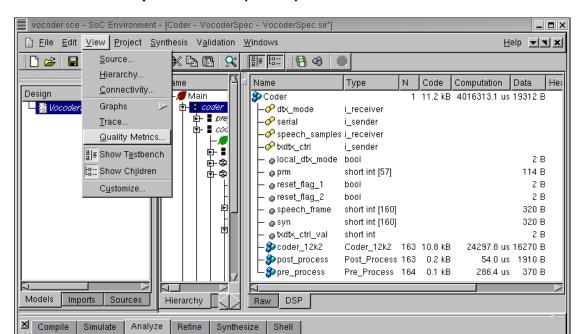

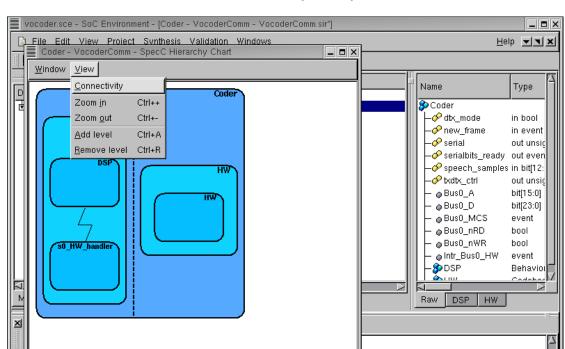

At this stage, we would like to delve into greater detail of the specification. To view the model graphically with higher detail, select View—Add level. Perform this action twice to get a more detailed view. As can be seen, the View menu provides features like displaying connectivity of behaviors, modifying detail level and zooming in and out to get a better view.

# 2.2.4.2. Browse specification model (cont'd)

Zoom out to get a better view by selecting View—>Zoom out

#### 2.2.4.3. Browse specification model (cont'd)

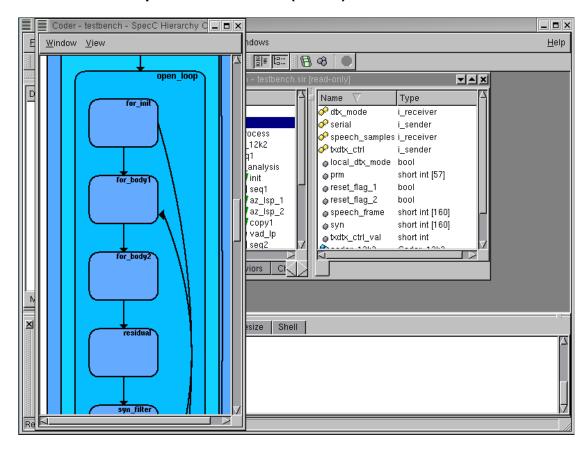

Scroll down the window to see the FSM and sequential composition of the Vocoder model. Note that the specification model of the GSM Vocoder does not contain much parallelism. Instead, many behaviors are sequentially executed. This is due to the several data dependencies in the code. For our implementation, this is an important observation. Since there is not much parallelism in the code to exploit, speedup can be achieved only by use of faster components. One way to speed up is to use dedicated hardware units.

Exit the hierarchy browser by selecting Window—→Close

We can also view the source of the models conveniently in SCE. For example, to check the source for behavior "coder", just click on the row in the hierarchy to select it. Then right click to bring up a menu and click on Source.

### 2.2.5.1. View specification model source code(cont'd)

```

vocoder.sce - SoC Environment

coder.sc - SpecC Editor

_ 🗆 ×

<u>F</u>ile <u>E</u>dit <u>S</u>earch <u>V</u>iew

void main(void)

□ {

#ifdef PIPED_CODER

pipe

/* filter + downscaling

pre_process.main();

/* Find speech parameters

coder_12k2.main();

/* insert comfort noise and convert parameters to serial bits */

post_process.main();

#else

fsm

⊟

/* filter + downscaling

pre_process:

/* Find speech parameters

coder_12k2:

/\ast insert comfort noise and convert parameters to serial bits \ast/ post_process: {

⊟

goto pre_process;

#endif

Line: 60 Col: 1

```

The SpecC Editor pops up containing the source code for the selected behavior. Changes to the source code can be made using the editor. After reviewing the source code, close the editor by selecting File—>Close from its menu bar.

# 2.3. Simulation and Analysis

Once we have captured the specification as a model and browsed through its behavioral hierarchy and connectivity, we need to ensure that our specification is correct. We also need to analyze our specification model to derive interesting observations about the nature of the computation. The check for correctness is done by simulating the model. Note that the model is purely functional, so the simulation runs very quickly. This is also a good time to debug the model for functional errors that might have crept in while writing it.

After the model is verified to be functionally correct, we proceed to the analysis phase. For this, we need to profile the model using the profiling tool available in SCE. The profile gives us useful information like the about of computation, its distribution over the various behaviors in the model and its nature. This information is need to make crucial architectural choices as we will see as the demo proceeds.

### 2.3.1. Simulate specification model

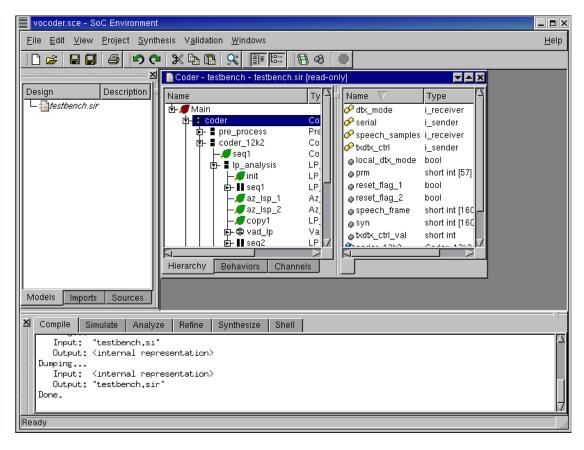

We must now proceed to validate the specification model. Remember that we have a "golden" output for encoding of the 163 frames of speech. The specification model would meet its requirements if we can simulate it to produce an exact match with the golden output. In practice, a more rigorous validation process is involved. However, for the purpose of the tutorial, we will limit ourselves to one simulation only. Start with adding the current design to our Vocoder project by selecting Project—Add Design from the menu bar.

# 2.3.1.1. Simulate specification model (cont'd)

The project is now added as seen in the project management workspace on the left in the GUI.

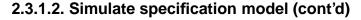

We must now rename the project to have a suitable name. Remember that our methodology involved 4 models at different levels of abstraction. As these new models are produced, we need to keep track of them. Right click on "testbench.sir" and select Rename to rename the design to "VocoderSpec". This indicates that the current model corresponds to the topmost level of abstraction, namely the specification level. Note that the extension ".sir" would be automatically appended. Also note that a model may be made activated, deleted, renamed and and its description modified by right click on its name in the project management window.

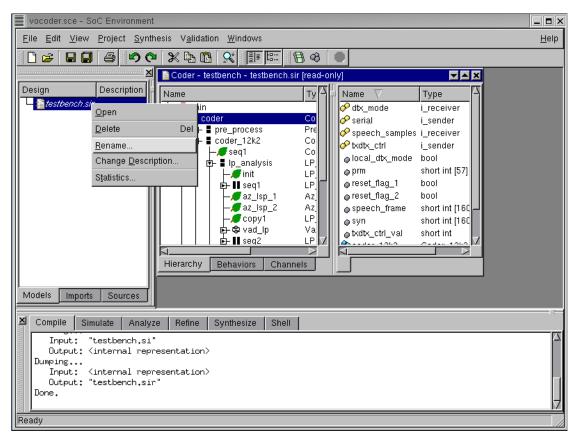

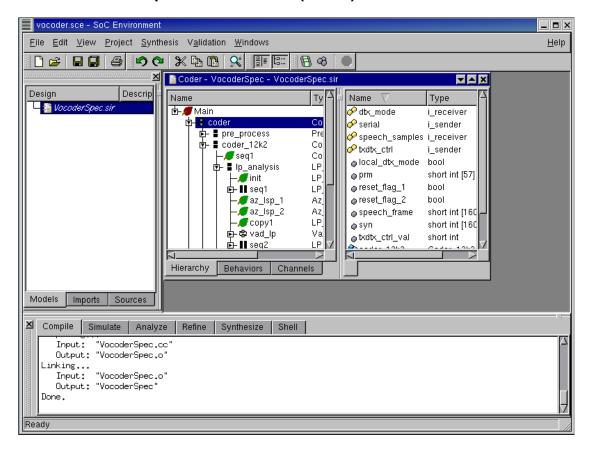

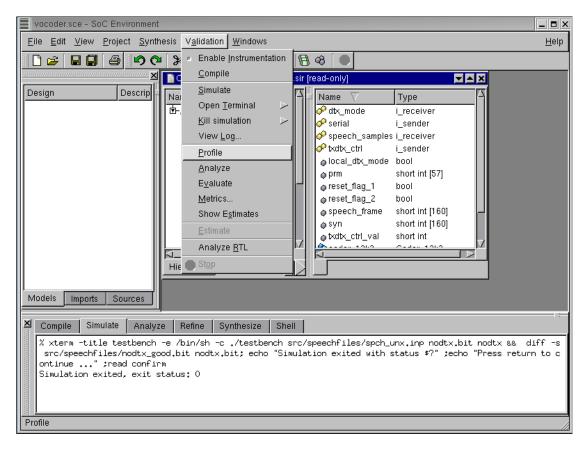

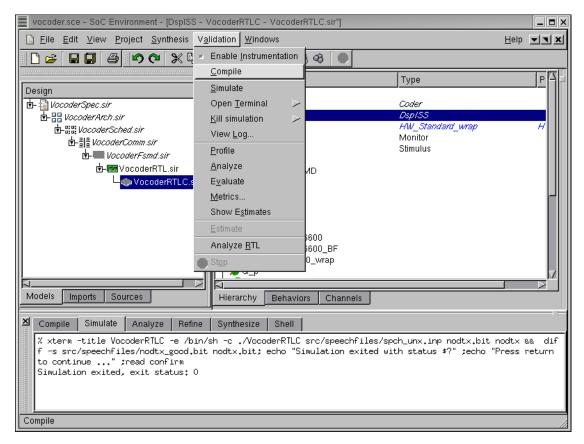

### 2.3.1.3. Simulate specification model (cont'd)

Compile

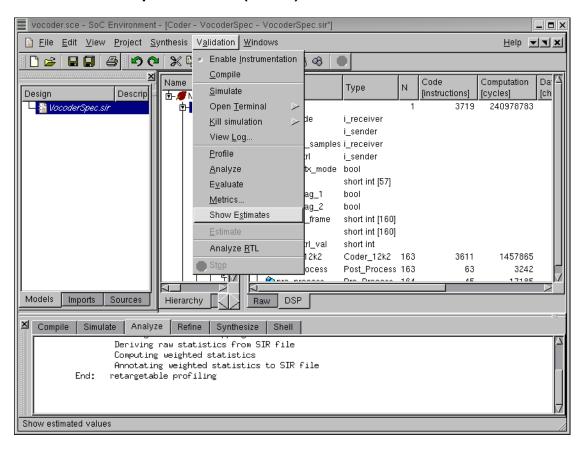

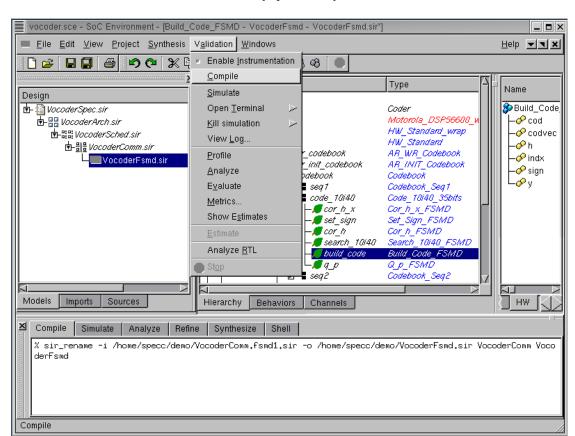

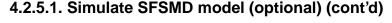

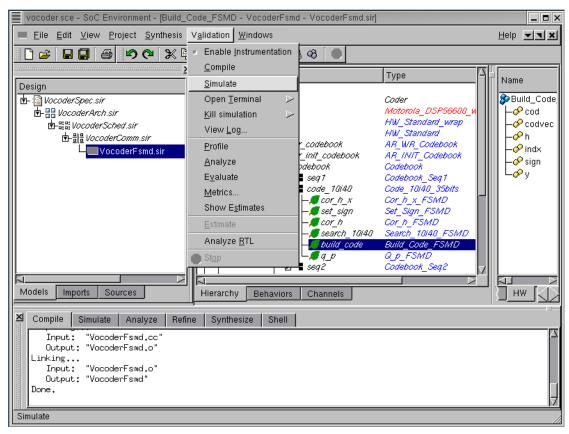

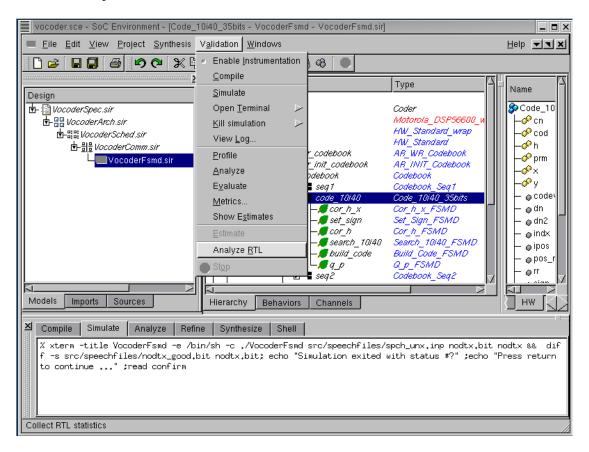

After the project is renamed to "VocoderSpec.sir", we need to compile it to produce an executable. This may be done by selecting Validation—Compile from the menu bar. Note that the validation menu also provides for code instrumentation which is used for profiling. Moreover, we have choices for simulating the model, opening a simulation terminal, killing a running simulation, viewing the log, profiling, analyzing simulation results, model evaluation, displaying metrics and estimates etc. All these features will be used in due course of our system design process.

# 2.3.1.4. Simulate specification model (cont'd)

Note that in the logging window we see the compilation messages and an output executable "VocoderSpec" is created.

# 2.3.1.5. Simulate specification model (cont'd)

Simulate

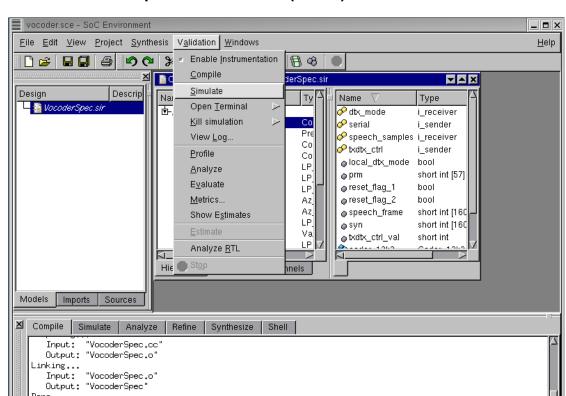

The next step is to simulate the model to verify whether it meets our requirements or not. This may be done by selecting Validation—Simulate from the menu bar.

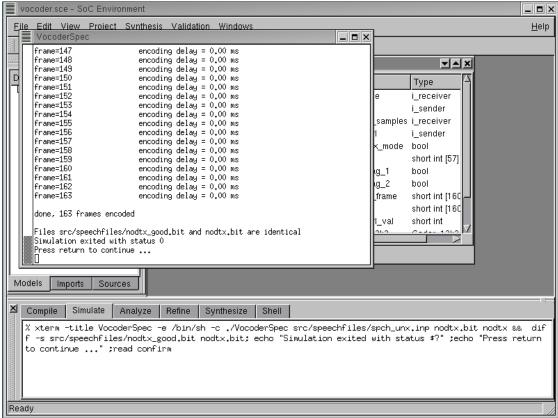

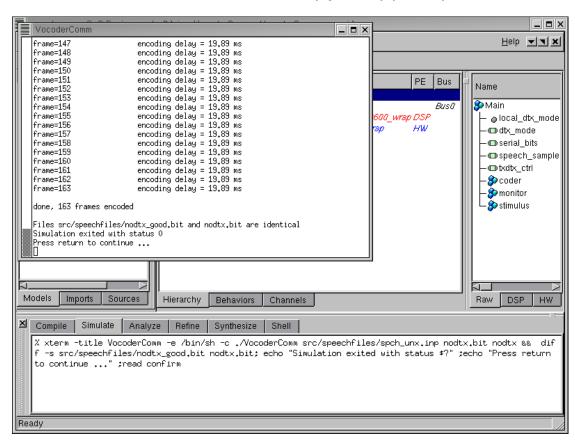

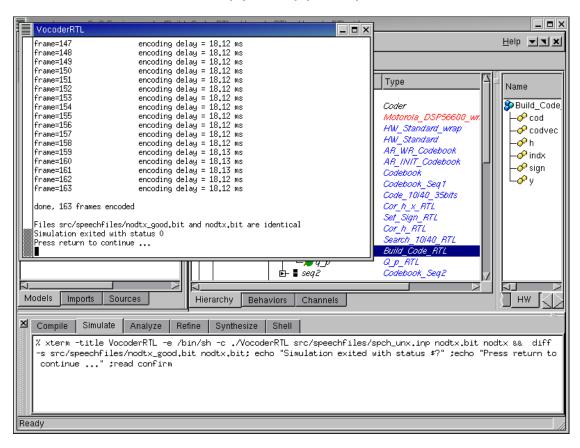

Note that an xterm pops up showing the simulation of the Vocoder specification model on a 163 frame speech sample. The simulation should finish correctly which is indicated by the exit status being '0'. It can be seen that 163 speech frames were correctly simulated and the resulting bit file matches the one given with the vocoder standard. It may be noted that each frame has an encoding delay of 0 ms. This is a because our specification model has no notion of timing. As explained in the methodology, the specification is a purely functional representation of the design and is devoid of timing. For this reason, all behaviors in the model execute in 0 time thereby giving an encoding delay of 0 for each frame. Press RETURN to close this window and proceed to the next step.

In order to select the right architecture for implementing the model, we must begin by profiling the specification model. Profiling provides us with useful data needed for comparative analysis of various modules in the design. It also counts the various metrics like number of operations, class and type of operation, data exchanged between behaviors etc. These statistics are collected during simulation. Profiling may be done by selecting Validation—>Profile from the menu bar.

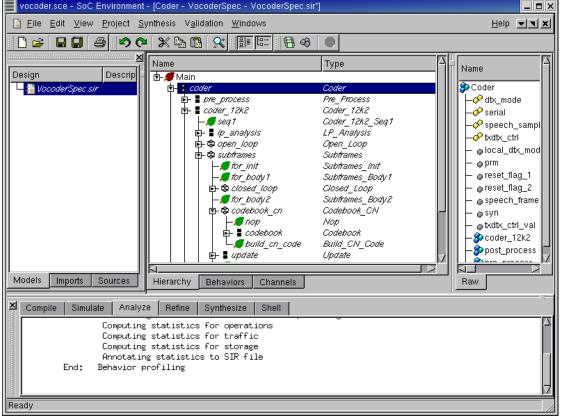

### 2.3.2.1. Profile specification model (cont'd)

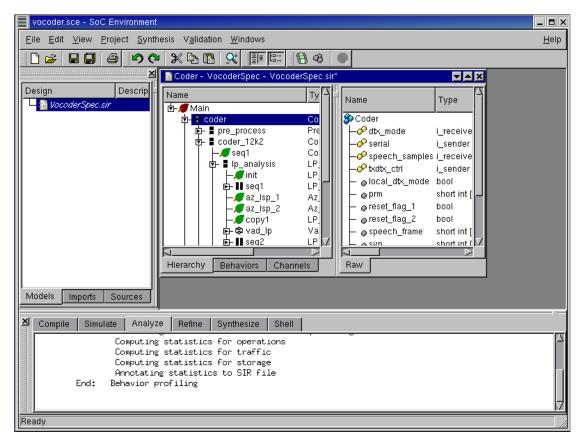

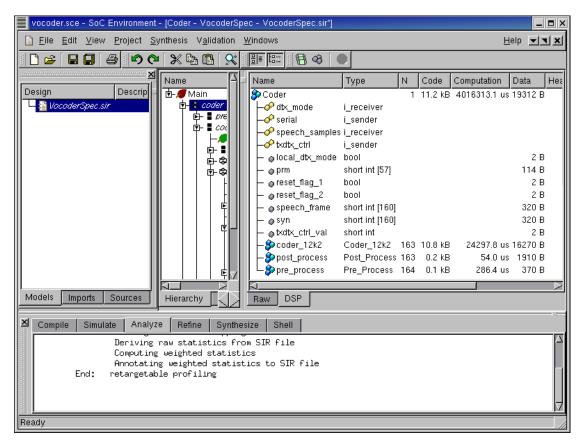

The logging window now shows the results of the profiling command. Note that there is a series of steps for computing statistics for individual metrics like operations, traffic, storage etc. Once these statistics are computed, they are annotated to the model and displayed in the design window.

### 2.3.2.2. Profile specification model (cont'd)

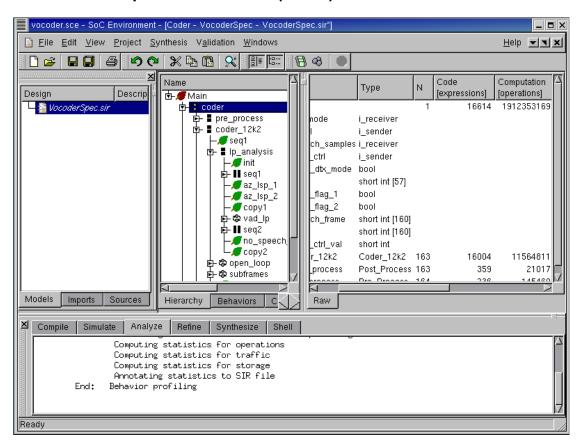

It may also be noted that the design management window now has new column entries that contain the profile data. Maximize this window and scroll to the right to see various metrics for behaviors selected in the design hierarchy. The current screen shot shows Computation, Data, Connections and Traffic for the top level behavior "coder". Computation essentially means the number of operations in each of the behaviors. Data refers to the amount of memory required by the behaviors. Connections indicate the presence of inter-behavior channels or connection through variables. Traffic refers to the actual amount of data exchanged between behaviors. The metrics may also be obtained for other behaviors in the design besides "coder".

# 2.3.3. Analyze profiling results

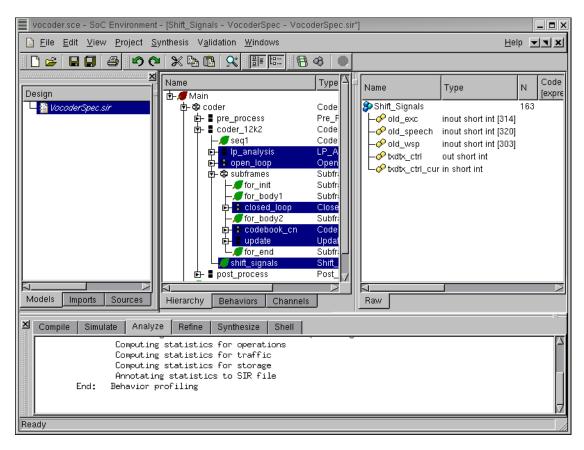

Once we have the profiling results, we need a comparative analysis of the various behaviors to enable suitable partitioning. Here we analyze the six most computationally intensive behaviors namely "lp\_analysis", "open\_loop", "closed\_loop", "codebook\_cn", "update" and "shift\_signals." They may be multi-selected in the design hierarchy by pressing CNTRL key and left clicking on them. These particular behaviors were selected because these are the major blocks in the behavior "coder\_12k2", which in turn is the central block of the entire coder. Thus the selected behaviors show essentially the major part of the activity in the coder. We ignore the pre-processing and the post-processing blocks, because they are of relatively lower importance.

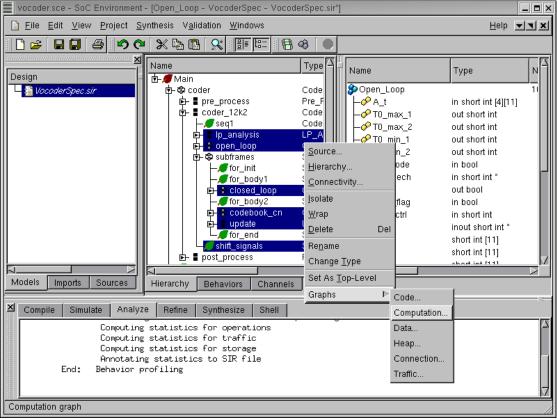

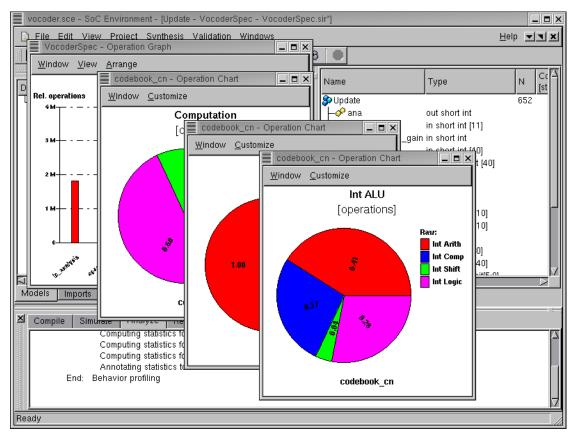

In order to select a suitable architecture for implementing the system, we must perform not only an absolute but also a comparative study of the computation requirements of the selected behaviors. SCE provides for graphical view of profiling statistics which may be used for this purpose. After the multi-selection, we right click and select Graphs——Computation from the menu bar.

### 2.3.3.2. Analyze profiling results (cont'd)

We now see a bar graph showing the relative computational intensity of the various behaviors in the selected behaviors. Essentially, the graph shows the number of operations on the Y-axis for the individual behaviors on the X-axis. Double click on the bar for codebook\_cn to view the distribution of its various operations. Note that we select "codebook\_cn" because it is the behavior with the most computational complexity.

Note that the bars representing the computation for "codebook\_cn" and "closed\_loop" have two sections. The lower section is filled with red color and the upper section is partially shaded. Each speech frame consists of four sub-frames and the behaviors "codebook\_cn" and "closed\_loop" are executed for each subframe in contrast to other behaviors in the graph, which are executed once. Hence the filled section of the bar represents computation for each execution of behavior and the complete bar (including the shaded section) represents computation for the entire frame.

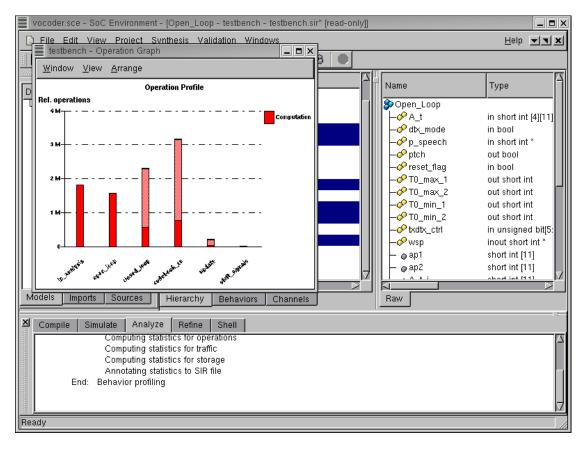

# 2.3.3.3. Analyze profiling results (cont'd)

A new window pops up showing a pie chart. This pie chart shows the distribution of various operations like ALU, Control, Memory Access etc. We are interested in seeing the types of ALU operation for this design. To do this double click on the ALU (green) sector of the pie chart.

### 2.3.3.4. Analyze profiling results (cont'd)

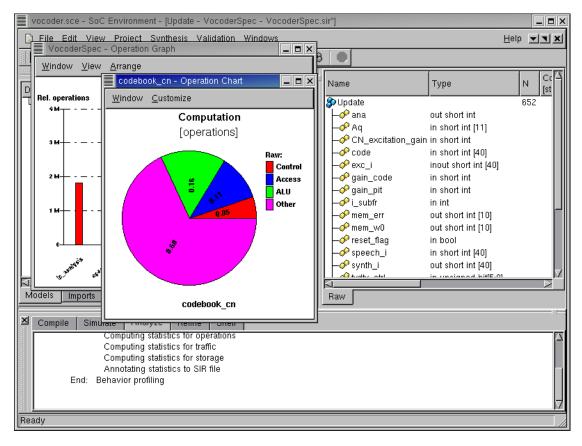

A new window pops up showing another pie chart. This pie chart shows the distribution of ALU operations. It can be seen that all the operations are integer operations, which is typical for signal processing application like the Vocoder. Since all the operations are integral, it does not make sense to have any floating point units in the design. Instead, we need a component with fast integer arithmetic like a DSP. To see the distribution of these integer operations, again double click on the pie chart.

# 2.3.3.5. Analyze profiling results (cont'd)

A new window pops up showing another pie chart. This pie chart shows the distribution of the type of integer operations. We can see that the majority of the operations is integer arithmetic. To view the distribution of the arithmetic operation types, again double click on the sector for "Int Arith".

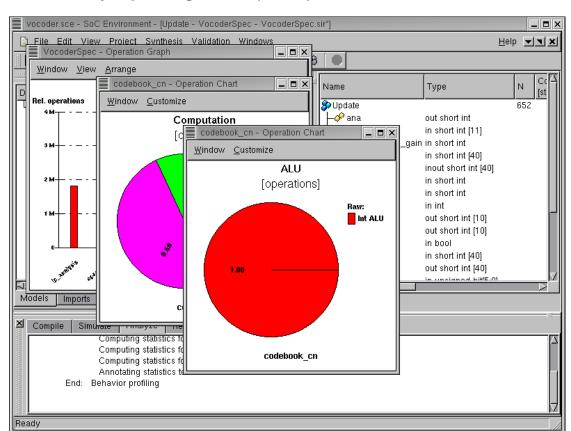

#### vocoder.sce - SoC Environment - [Update - VocoderSpec - VocoderSpec.sir\* File Edit View Project Synthesis Validation Windows Help ▼▼× \_ 🗆 × VocoderSpec - Operation Graph Arrange Cc A codebook\_cn - Operation Chart \_ **-** × Name [st Rel. operations Window Customize By Update 652 🔗 ana out short int Computation codebook\_cn - Operation Chart in short int [11] \_ 🗆 × ain in short int Window Customize codebook\_cn - Operation Chart \_ | **-**| × Window Custo codebook\_cn - Operation Chart \_ 🗆 × Window Customize Int Arith [operations] S. Carlot 1.00 Models /,long -,int p++,int Computing statistics t p--,int Computing statistics for Computing statistics for others Annotating statistics End: Behavior profiling codebook cn

### 2.3.3.6. Analyze profiling results (cont'd)

We can now observe the distribution of arithmetic operations like "multiplication", "addition", "increment", "decrement", etc. on a new pie chart. Note that 3 quarters of the operations are additions or multiplications, thus it would be a good idea to have these two operations directly supported by a specific hardware unit.

The combination of visual aids like bar graphs and pie charts gives a good idea of the nature of intended system. Please close all the pop-up windows to conclude the specification analysis phase.

# 2.4. Summary

In this chapter we looked at how to start with the system specification and analyze its characteristics. We were familiarized with the SCE graphical user interface and the profiling, analysis and simulation tools. By means of graphical tools, we were able to traverse the hierarchy of the system specification model. Graphical representations also provided us with information on connectivity between behaviors in the design. The user friendliness of these representations allows us to analyze our design better which would otherwise be very cumbersome.

Profiling and statistical data about the specification model also gives us interesting hints. For instance, the nature of computation in the model shows us the appropriate components to consider for the system architecture. Similarly, pie charts and bar graphs for the distribution of computation show us the critical behaviors and their nature. As we move forward in the system design process, we will have to make design decisions at various stages and such statistical analysis will be of great value. In future implementations on the tool, these analysis results may even be fed to automatic tools to generate optimal system architectures.

Chapter 2. System Specification Analysis

# Chapter 3. System Level Design

### 3.1. Overview

Figure 3-1. System level design phase using SCE

System design is increasingly being performed at higher levels of abstraction to deal with a variety of issues. In this chapter, we look at system level design tasks with SCE as highlighted in figure 3-1. Firstly, we need to deal with both HW and SW in a single model. Secondly, and more importantly, complexity becomes unmanageable. In this chapter we will look at the system level design phase as shown in the above figure. This phase comprises of architecture exploration, serialization/RTOS insertion and communication synthesis. Architecture exploration deals with coming up with a suitable system architecture and distributing the system tasks in the specification onto those components. Since each component has a single control, we need to serialize the tasks in each component. Tasks that are mapped to SW can be dynamically scheduled on the processor by inserting an RTOS model. Finally, we perform communication synthesis to come up with a communication architecture and refine the data transfer and interfaces to use the

# Chapter 3. System Level Design

communication architecture. The goal of this phase is to come up with a model that can serve as an input to RTL synthesis for HW components and SW generation for processors.

# 3.2. Architecture Exploration

Architecture exploration is the design step to find the system level architecture and map different parts of the specification to the allocated system components under design constraints. It consists of the tasks of selecting the target set of components, mapping behaviors to the selected components and implementing correct synchronization between the components. Note that the components themselves are independent entities that execute in a parallel composition. In order to maintain the original semantics of the specification, the components need to be synchronized as necessary. Architecture exploration is usually an iterative process, where different candidate architectures and mappings are experimented to search for a satisfactory solution.

As indicated earlier, the timing constraint for the Vocoder design is the real time response requirement, i.e., the time to encode and decode the speech should be less than the speech time. The test speech has a 3.26 seconds duration. Therefore, the final implementation must meet this time constraint. In this chapter we see how we arrive at a suitable architecture with keeping this requirement in mind and using the refinement tool.

# 3.2.1. Try pure software implementation

The goal of our exploration process is to implement the given functionality on a minimal cost architecture and still meet the timing constraint. The first approach is to implement everything in software so that we do not have the overhead of adding extra hardware and associated interfaces. To accomplish this, we first select a processor out of our component database. Thereafter, we map the entire specification on to this processor. Once the mapping is done, we invoke the analysis tool to see if the processor alone is sufficient to implement the system.

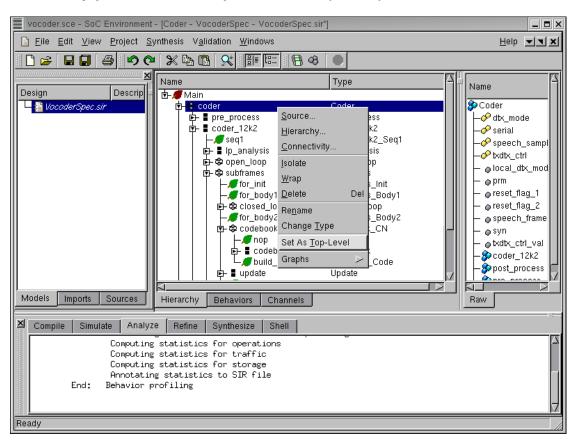

### 3.2.1.1. Try pure software implementation (cont'd)

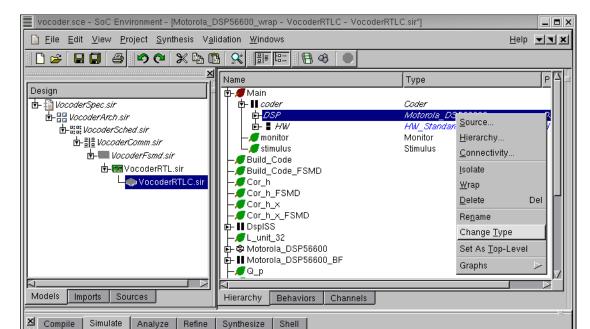

Before we move on, the top level behavior of the design needs to be specified. This is necessary because the specification model may have some test bench behaviors, which are not going to be included in the final design. It may be recalled that the project we are working with involves not only the design-under-test (DUT) but also the behaviors that drive it. For example, the behaviors "Monitor" and "Stimilus" are just testbench behaviors while the behavior "Coder" represents the real design. To specify "Coder" as the top level behavior, right click on "Coder" to bring up a drop box menu then left click on Set As Top-Level.

As shown in the figure, when the top level behavior "Coder" is specified, the names of all its child behaviors are italicized to distinguish them from the test bench behaviors. In general, any behavior which needs to be tested can be set as top level. So, in a generic sense, the design under test can be identified by the italicized font.

### 3.2.1.3. Try pure software implementation (cont'd)

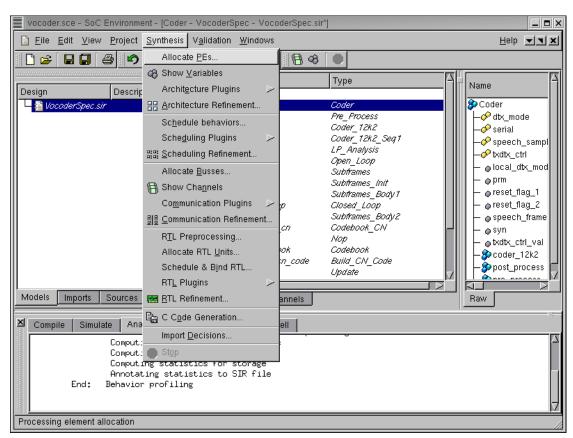

We begin by exploring the available set of components in the database. This is required to select a suitable processor. To view all available components and select the desired processor, select Synthesis—Allocate PEs... from the menu bar.

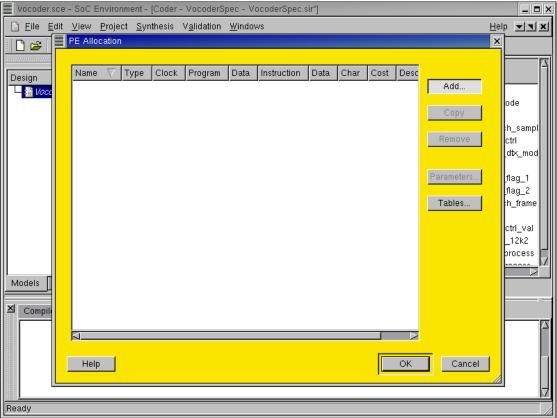

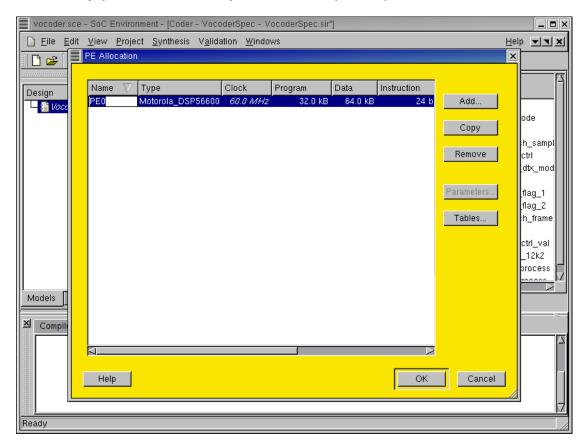

Now a PE Allocation window pops up. This window includes a table to display important characteristics of components selected for the design. In addition, it also provides a number of buttons (on the right side) for user actions, such as adding a component, removing a component, and so on. Since we have not allocated any component at this point, the table has no entry.

To view the component database and select the desired component, press the Add... button.

### 3.2.1.5. Try pure software implementation (cont'd)

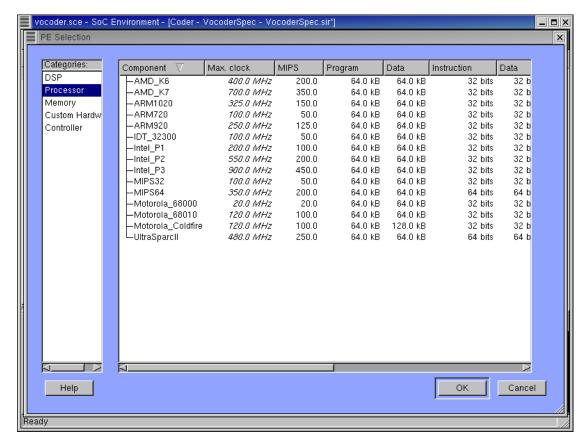

Now a PE Selection window is brought up. The left side of the window (Categories) lists five categories of components stored in the database. The right side of the window displays all components within a specific category along with their characteristics. As shown in the above figure, since the Processor category is selected on the left side, 15 commonly used processor components are displayed in detail on the right side.

The Component description includes features like maximum clock speed, measure of the number of instructions per second, a cost metric, cache sizes, instruction and data widths and so on. These metrics are used for selecting the right component. Remember that the profiling data has given us an idea of what kind of component would be suitable for the application at hand.

# 3.2.1.6. Try pure software implementation (cont'd)

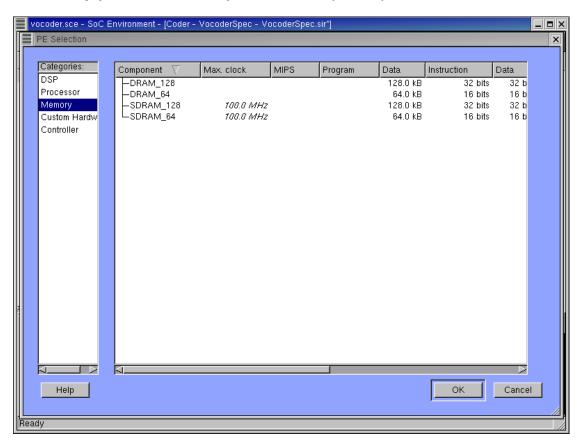

Now if we go to the Mem category, a number of memory components will be displayed in detail on the right side of the window. If the memory in the processor is insufficient for the application, we can add external memory components from this table.

# 3.2.1.7. Try pure software implementation (cont'd)

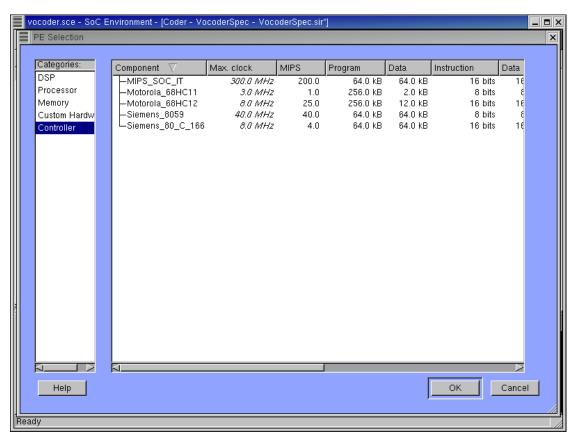

Now if we go to the Controller category, a number of widely used micro-controller components will be displayed in detail on the right side of the window.

### 3.2.1.8. Try pure software implementation (cont'd)

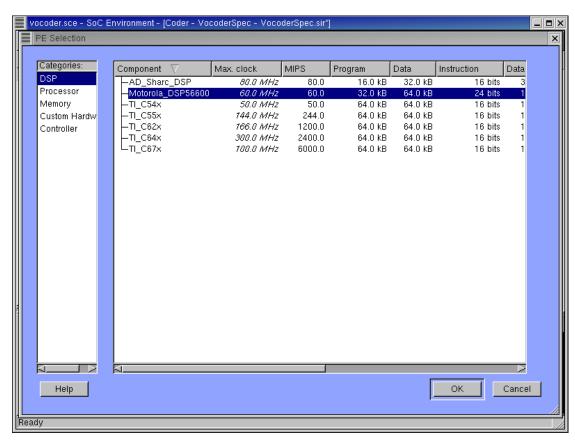

Through earlier profiling and analyzing, we found out that integer multiplication is the most significant operations in the original specification. Therefore, a fixed-point DSP would be desirable for this design.

Under the DSP category, a number of commercially available DSPs are displayed. These DSP components are maintained as part of the component library and may be imported into the design upon requirement. Since the Vocoder design project was supported by Motorola, our first choice is DSP56600 from Motorola.

Left click the "Motorola\_DSP56600" row to select it. Then click **OK** button to confirm the selection.

### 3.2.1.9. Try pure software implementation (cont'd)

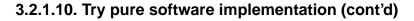

Now the PE Selection window goes away and the PE Allocation table has one row that corresponds to our selected component, which has a type of "Motorola\_DSP56600". This new component was named as "PE0" by default. To make it more descriptive for later reference, it is desirable to rename it.

To rename it, just left click in the Name column of the row. The cursor will be blinking to indicated that the text field is ready for editing.

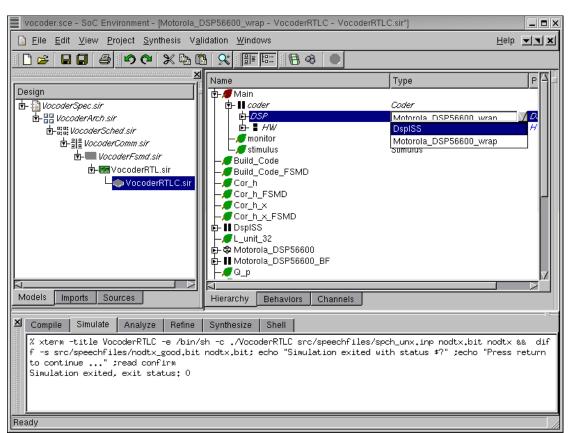

We will simply name the component as "DSP" since it is the only component used in the design at this instance. Proceed by typing "DSP" in the text field and press return to complete the editing. Then press the OK to finish component allocation.

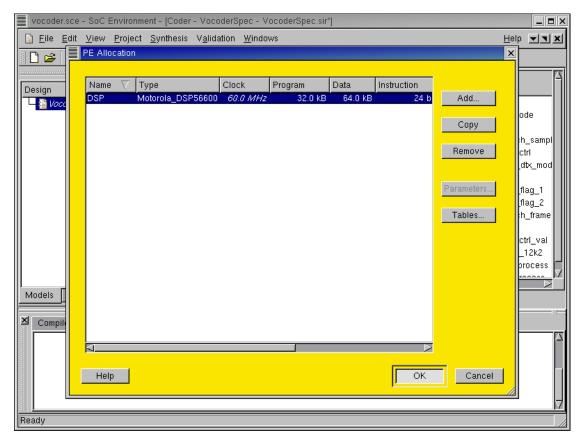

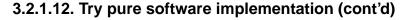

### 3.2.1.11. Try pure software implementation (cont'd)

As mentioned earlier, we will map the whole design to the selected processor. This is done by assign the top level behavior "Coder" to "DSP". Left click in the PE column in the row for the "Coder" behavior. A drop box containing allocated components comes up. Left click on "DSP" to map behavior "Coder" to "DSP".

It should be noted that any kind of mapping is allowed. However, since we are investigating a purely software implementation, everything in the design gets mapped to the "DSP".

As we can see now, the descendant behaviors are all highlighted in red to indicated that they are mapped to the "DSP" component.

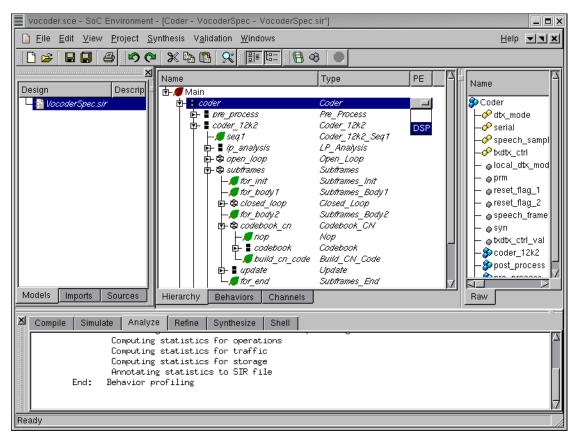

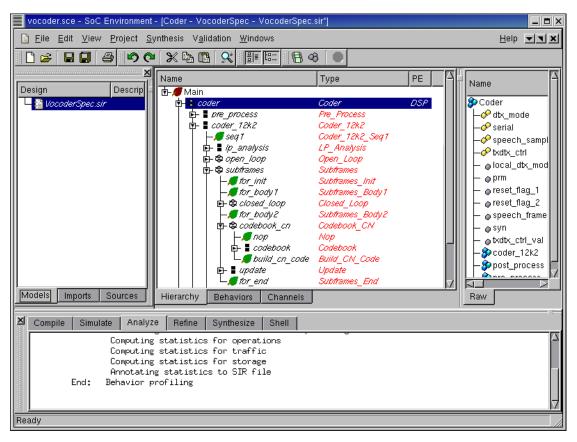

# 3.2.2. Estimate performance

The next step is to analyze the performance of this architecture. Recall that we have a timing constraint to meet. We must therefore check if a purely software implementation would still suffice. If not, we will try some other architecture. Now we can estimate the performance of this pure software mapping by selecting Validation—>Evaluate from the menu bar.

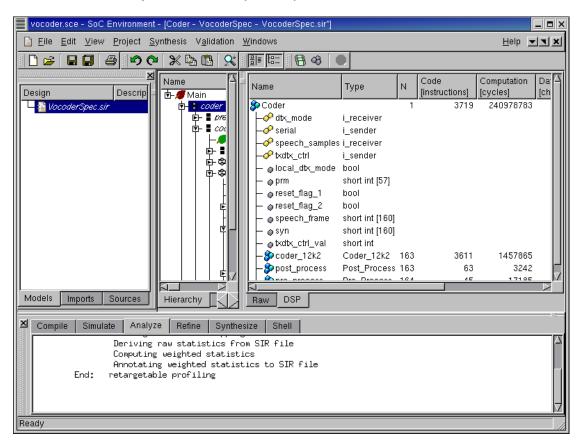

As we can see in the logging window, a re-targeted profiling is being performed. Notice in the log information that raw statistic generated during profiling are used here. The raw statistics are take as an input to the analysis tool that generates statistics for the current architecture. Since, we know the parameters of the DSP, the analysis tool can provide a more accurate measure of actual timing. When that is done, the profiled data is displayed in the design window with the "DSP" tab. Notice that this tab has appeared at the bottom of the design data. The total computation time is shown in terms of number of DSP clock cycles.

### 3.2.2.2. Estimate performance (cont'd)

The number of computation cycles is a relevant metric for observation. However, it must be converted to an absolute measure of time so that we may directly verify if this architecture meets the demands. To find out the real execution time in terms of seconds, we turn on the option for estimation by selecting Validation—Show Estimates from the menu bar.

As seen in the design window, the computation time is in unit of "us". As we can see in the row of behavior "Coder", the estimated execution time ( $\sim 4.00$  seconds) exceeds the timing constraint of 3.26 seconds.

## 3.2.2.4. Estimate performance (cont'd)

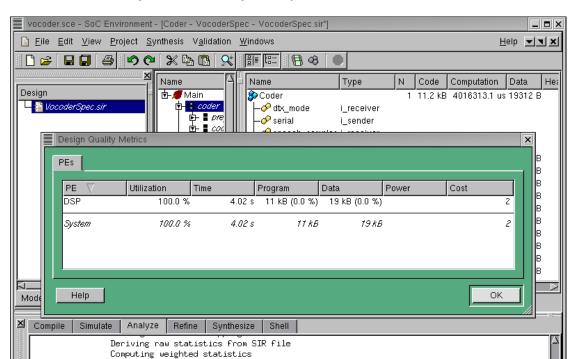

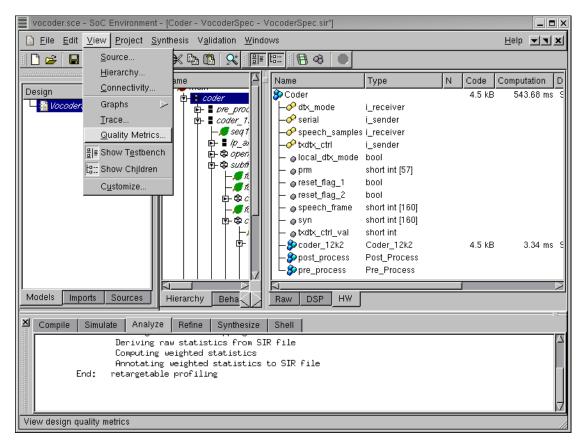

We can also view the design quality metrics such as the execution time by selecting  $View \longrightarrow Quality$  Metrics from the menu bar.

Deriving raw statistics from SIR file Computing weighted statistics

retargetable profiling

View design quality metrics

Annotating weighted statistics to SIR file

### 3.2.2.5. Estimate performance (cont'd)

A Design Quality Metrics table pops up, showing that the estimated execution time to be 4.02 seconds, which exceeds the timing constraint of 3.26 seconds. Therefore, the pure software solution with a single "Motorola\_DSP56600" does not work. We, therefore, need to experiment with other architectures. To proceed, click OK to close the Design Quality Metrics table.

Annotating weighted statistics to SIR file

retargetable profiling

Ready

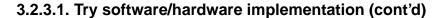

# 3.2.3. Try software/hardware implementation

From what we observed while studying the vocoder specification, the design is mostly sequential. There is not much parallelism to exploit. What we need to reduce the execution time is a much faster component than the DSP we used. Some of the critical time consuming tasks may be mapped to a fast hardware. In this iteration, we will try to add one hardware component along with the DSP to implement the design. As we found out earlier, one of the computationally intensive and critical part in the Vocoder is the Codebook behavior. We hope to speed it up by mapping it to a custom hardware component and execute the remaining behaviors on the DSP.

As we did earlier, while selecting the processor, go to Synthesis—Allocate PEs... on the menu bar.

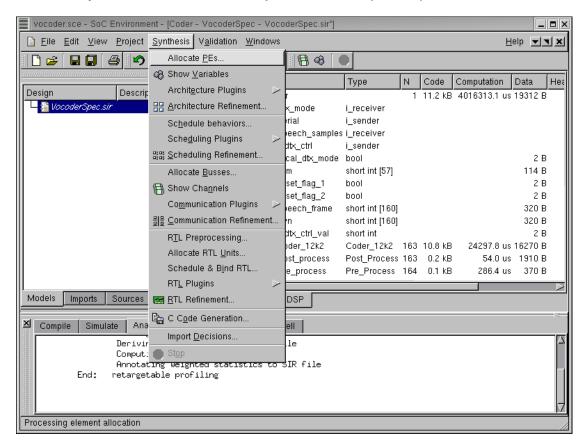

# 3.2.3.2. Try software/hardware implementation (cont'd)

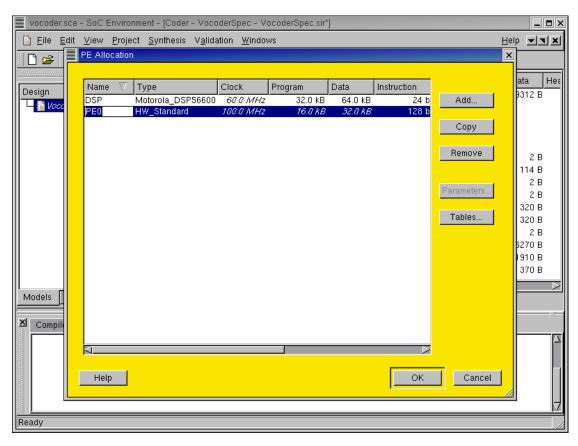

This time, the PE Allocation table pops up. As we can see, the previously allocated "DSP" component is displayed. To insert the hardware component, press Add... button to go to component database.

# 3.2.3.3. Try software/hardware implementation (cont'd)

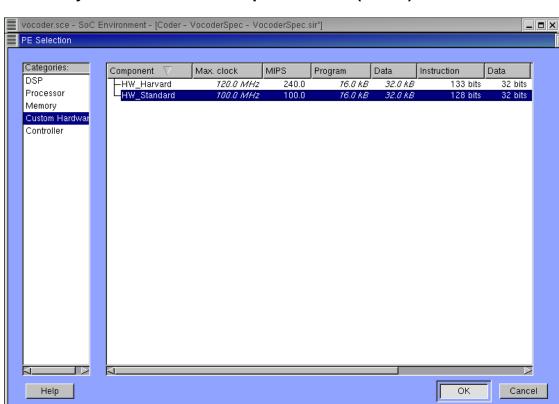

In the Custom Hardware category, two general types of hardware components are displayed. Here we will use the standard hardware design with a datapath and a control unit. Select the "HW\_Standard" and press OK to confirm the selection.

Ready

## 3.2.3.4. Try software/hardware implementation (cont'd)

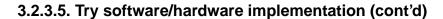

Now the "HW\_Standard" component is added to the PE Allocation table. In the same way we did for the "DSP" component, we simply rename it to "HW" to distinguish it. Notice that for the hardware component, some metrics are flexible. For instance, the clock period may be changed. However, we stay with the current speed of 100 Mhz for demo purpose.

After we renamed it, press OK button to complete component allocation.

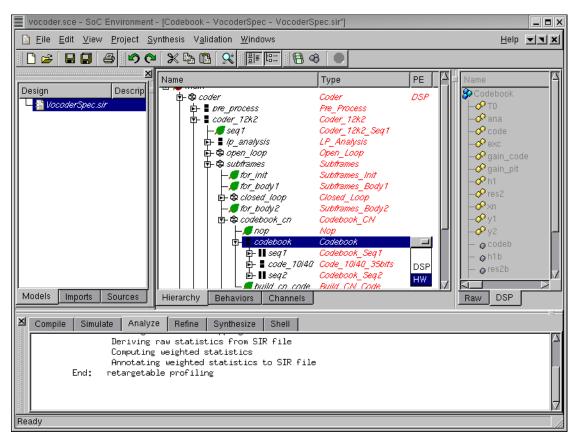

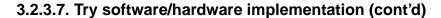

## 3.2.3.6. Try software/hardware implementation (cont'd)

Remember we have already specified the top level behavior and mapped all behaviors to "DSP" in the first iteration. That information is still there and we do not have to specify it again. We only need to map behavior "Codebook" to the "HW" component, as suggested earlier.

Browse the hierarchy tree to locate behavior "Codebook". Click on "Codebook" in the PE column. Click on "HW" in the drop box to map "Codebook" to "HW". This would map the entire subtree of behaviors under "Codebook" to custom hardware.

After the mapping, we will see the subtree rooted at "Codebook" is highlighted in blue in contrast to the rest behaviors in red that are mapped to "DSP".

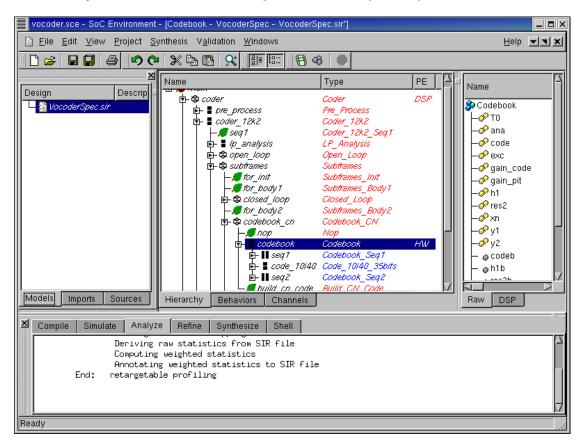

# 3.2.4. Estimate performance

It may be recalled that we abandoned the pure software implementation because it failed on meeting the timing constraint. It is now time for us to verify if the timing is met by using the combined software/hardware design. To evaluate this software and hardware implementation, go to Validation—>Evaluate on the menu bar.

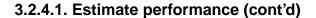

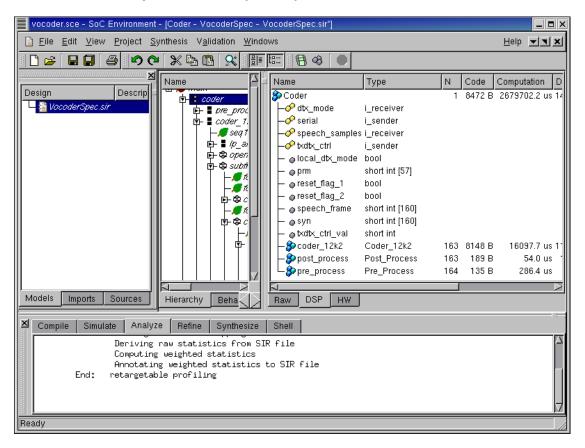

As we can see in the logging window, a profiling re-targeted at the DSP and HW architecture is being performed. When it finishes, the profiled data is presented in the design window. In order to find out the execution time of the Coder, select Coder behavior in the hierarchy tree. By clicking on the DSP tab of the view-pane, information of the DSP part of "Coder" behavior is displayed. For example, the execution time of the software part on DSP is around 2.68 seconds.

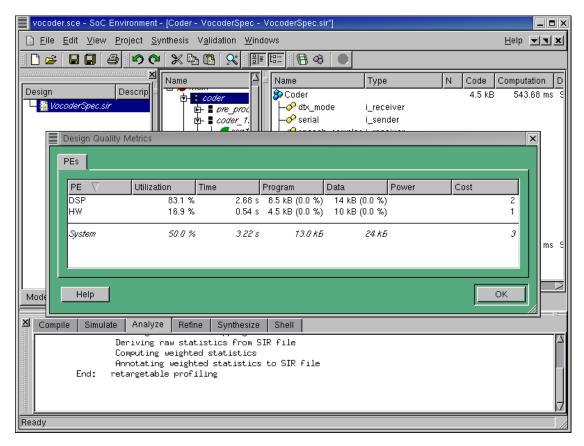

To find out the information on hardware side, click the HW tab. The view-pane shows that the execution of hardware part, behavior "Codebook", takes 0.54 seconds. Since "Codebook" was executed in sequential composition with the rest of the design, the latency of the design is the sum of DSP and HW execution time, which is 3.22 (2.68 + 0.54) seconds. Recall that the timing requirement is to be less than 3.26 seconds for the given speech data. Therefore, the current architecture and mapping are acceptable.

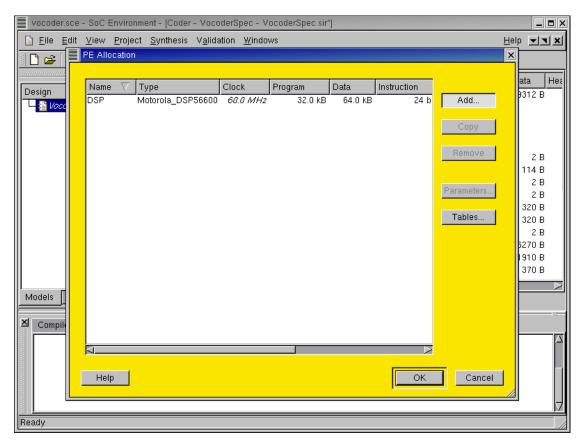

Like we did earlier, we can also view the execution time in the Design Quality Metrics table. To do so, select View—Quality Metrics from the menu bar.

### 3.2.4.4. Estimate performance (cont'd)

As shown in the figure, the Design Quality Metrics table including a number of design quality metrics is displayed. It confirms that the total execution time is 3.22 seconds, same as what we figured out earlier. After reviewing the quality metrics, click on OK to close the table.

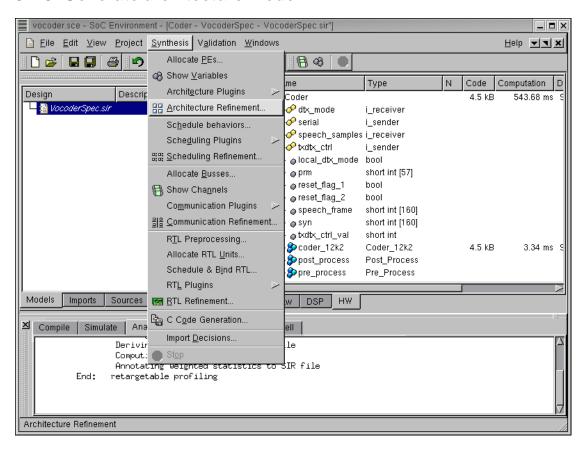

### 3.2.5. Generate architecture model

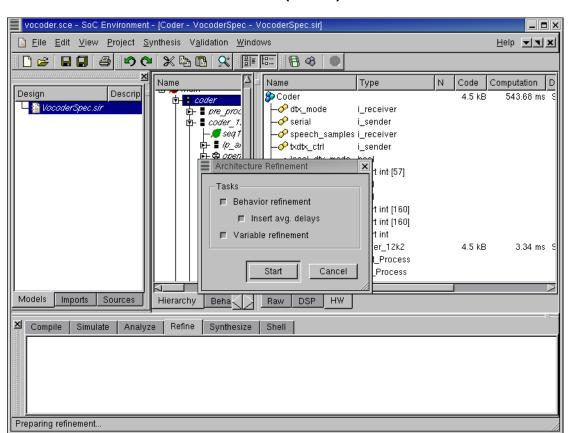

Now we can refine the specification model into an architecture model, which will exactly reflect the this architecture and mapping decisions. This can be done either manually or automatically. As we mentioned earlier, an architecture refinement tool is integrated in SCE. To invoke the tool, go to Synthesis—Architecture Refinement.... The tool changes the model to reflect the partition we created and also introduces synchronization between the parallely executing components. Note that we have not decided to map variables explicitly to components. For demo purposes, we will leave this decision to be made automatically by the refinement tool. However, it needs to be mentioned that the designer may choose to map variables in the design as deemed suitable.

## 3.2.5.1. Generate architecture model (cont'd)

A dialog box pops up for selecting specific refinement tasks of architecture refinement. By default, all tasks will be performed in one go. Now press the Start button to start the refinement. It must be noted that the user has an option to do the architecture refinements one step at a time. For instance, a designer may want to stop at behavior refinement if he is not primarily concerned about observing the memory requirements or the schedule on each component. Nevertheless, in our demo we perform all steps to generate the final architecture model.

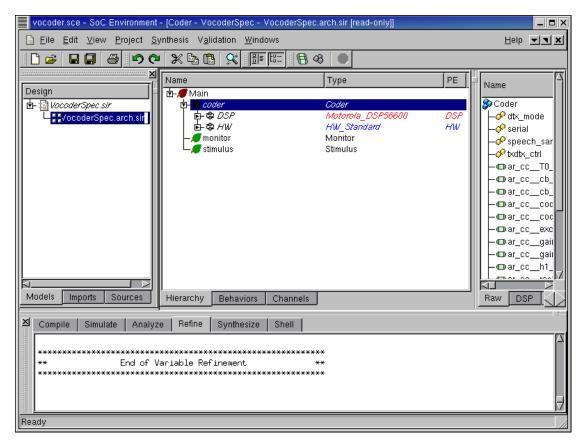

As displayed in the logging window, the architecture refinement is being performed. After the refinement, the newly generated architecture model "VocoderSpec.arch.sir" is displayed to the design window. It is also added to the current project window, under the specification model "VocoderSpec.sir" to indicate that it was derived from "VocoderSpec.sir". Please note that, while the architecture refinement only took a few seconds to generate, a whole new model has been created.

#### 3.2.6. Browse architecture model

In this section we will look at the architecture model to see some of its characteristics.

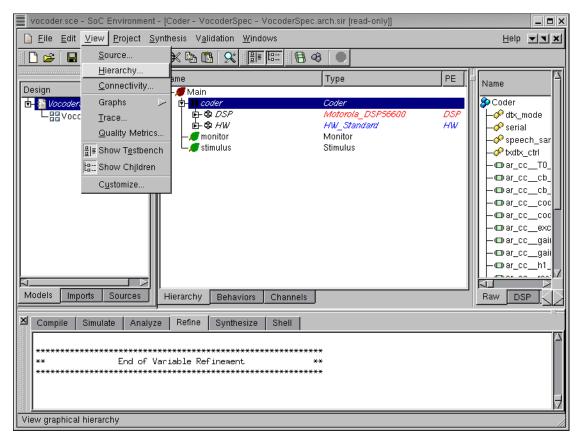

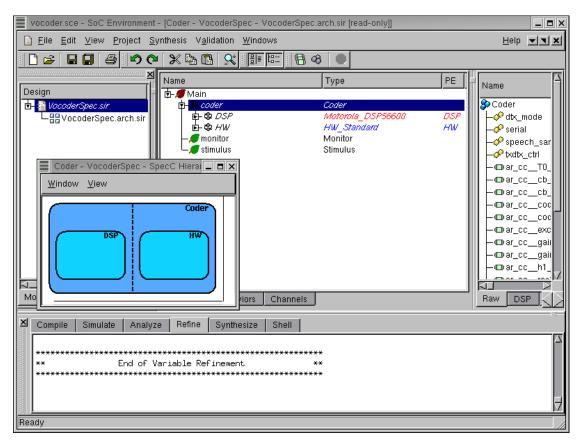

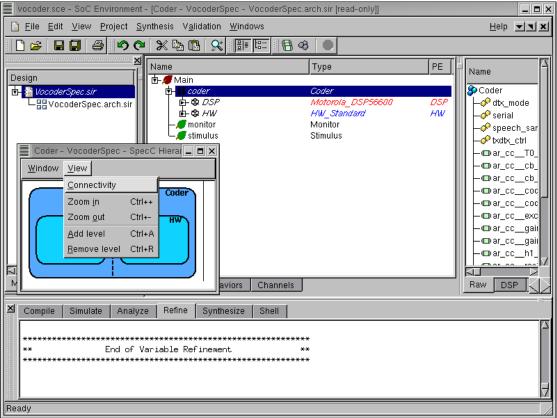

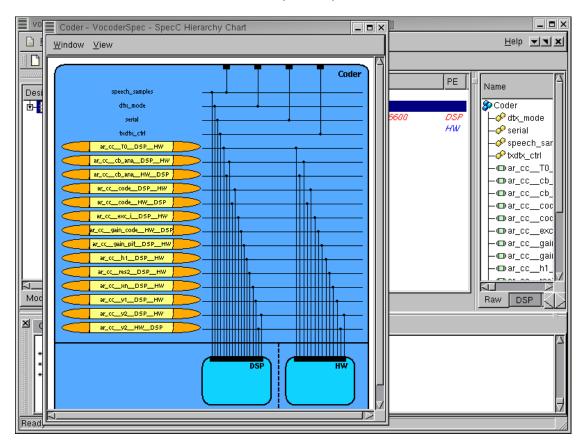

Since the top level behavior is "Coder", the test bench behaviors are not changed during architecture refinement. Therefore let's select "Coder" by clicking in the corresponding row in the design window. We would like to see how the design looks when it is mapped to the selected architecture. To view the hierarchy of the new "Coder" behavior, go to View—>Hierarchy....

A window pops up, showing all sub-behaviors of the "Coder" behavior. As we can see, this new top level behavior Coder in the architecture model is composed of two new behaviors, "DSP" and "HW", which were constructed and inserted during architecture refinement. These behaviors at the top level indicate the presence of two components selected in the architecture. Note that they are also composed in parallel, which represents the actual semantics of the architecture model.

We would now like to see how the "DSP" and "HW" behaviors are communicating. This will verify if the refinement process was correctly executed. Go to  $View \longrightarrow Connectivity$  to see the connectivity between the "DSP" and the "HW" components.

### 3.2.6.3. Browse architecture model (cont'd)

Enlarge the new window and scroll down to view the connectivity of the two components. We can see that "DSP" and "HW" components are connected through global variable channels, which were inserted during the architecture refinement. This is different from the original specification model, where only global variables were used for communication.

After checking the new architecture model, we can close the pop up window and go back to the design window by selecting Window—Close from the menu bar.

#### 3.2.6.4. Rename architecture model

Like what we did for the specification model, we also change the name of the new model to be "VocoderArch.sir" in the project window. The renaming is just for the purpose of maintaining a nomenclature schema and to correctly identify the individual models.

## 3.2.7. Simulate architecture model (optional)

This section shows the simulation of the generated architecture model. If the reader is not interested, she or he can skip this section and go directly to Section 3.3 *Software Scheduling and RTOS Model Insertion* (page 95).

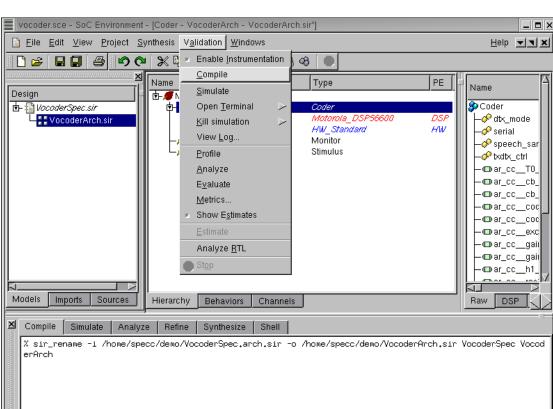

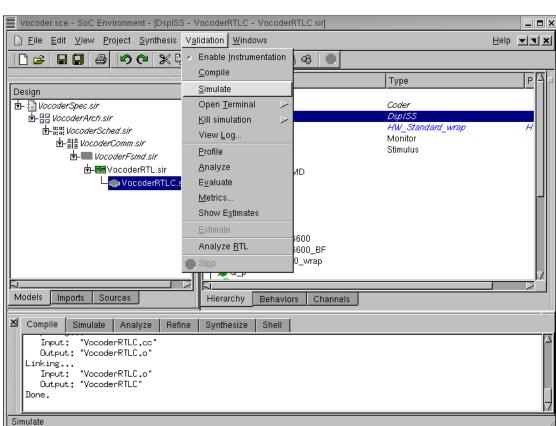

So far we have graphically visualized the automatically generated architecture. We have seen that in terms of its structural composition, the model meets the semantics of an architecture level model in our SoC methodology. However, we also need to confirm that the model has not lost any of its functionality in the refinement process. In other words the new model must be functionally equivalent to the specification. We will validate the architecture model through simulation. But first we need to compile the model into an executable. To compile the architecture model to executable, select Validation—>Compile from the menu bar.

Compile

### 3.2.7.1. Simulate architecture model (optional) (cont'd)

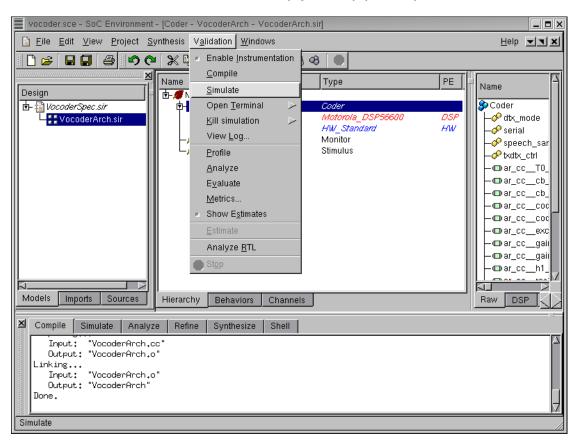

The messages in the logging window show that the architecture model is compiled successfully without any syntax error. Now in order to verify that it is functionally equivalent to the specification model, we will simulate the compiled architecture model on the same set of speech data used in the specification validation by selecting Validation—Simulate from the menu bar.

## 3.2.7.2. Simulate architecture model (optional) (cont'd)

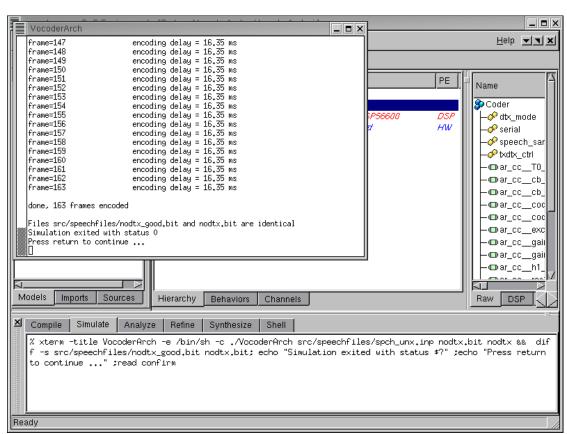

The simulation run is displayed in a new terminal window. As we can see, the architecture model was simulated successfully for all 163 frames speech data. The result bit file is also compared with the expected golden output given with the Vocoder standard. We have thus verified that the generated architecture model is functionally correct. In addition, the simulation of the architecture model shows that the processing time for each frame is 16.35 ms, which was not available when simulating the specification model.

It must be noted as before that the testing process requires fairly intensive execution, but for the demo purposes we will omit multiple simulations and just show the concept. This concludes the step of architecture exploration.

# 3.3. Software Scheduling and RTOS Model Insertion

The next step in the system level design process is the serialization of behavior execution on the processing elements. Processing elements (PEs) have a single thread of control only. Therefore, behaviors mapped to the same PE can only execute sequentially and have to be scheduled. Software scheduling and RTOS model insertion is the design step to schedule the behaviors inside each PE.

Depending on the nature of the PE and the data inter-dependencies, behaviors are scheduled statically or dynamically. In a static scheduling approach, behaviors are executed in a fixed and predetermined order, possibly flattening parts of the behavioral hierarchy. In a dynamic scheduling approach on the other hand, the order of execution is determined dynamically during runtime. Behaviors are arranged into potentially concurrent tasks. Inside each task, behaviors are executed sequentially. A RTOS model is inserted into the design. The RTOS model maintains a pool of task behaviors and dynamically selects a task to execute according to its scheduling algorithm. In this chapter we see how we make scheduling decisions using SCE.

## 3.3.1. Serialize behaviors

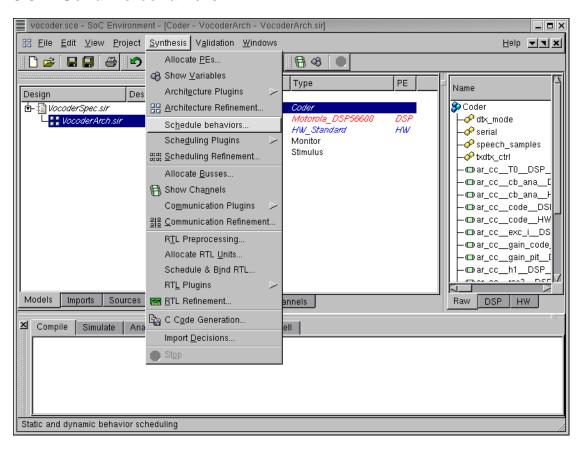

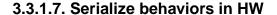

To start behavior scheduling, select Synthesis—Schedule behaviors from the menu bar.

#### 3.3.1.1. Schedule software

A Scheduling window will pop up. This window includes scheduling options for two PEs (DSP and HW). We begin by selecting the scheduling algorithm for the software. We can do either static scheduling or dynamic scheduling for the software. In case of dynamic scheduling, a RTOS model corresponding to the selected scheduling strategy is imported from the library and instantiated in the PE. The RTOS model provides an abstraction of the key features that define a dynamic scheduling behavior independent of any specific RTOS implementation. SCE provides two RTOS models with different dynamic scheduling algorithms: round-robin and priority based.

Behavior scheduling is done by converting all concurrent SpecC "par" or "pipe" statements into sequential statements. This conversion is achieved by performing the "serialize" operations on the intended behaviors. For example, assume that behavior "A" is a "par" composition of behavior "B" and "C". With a "serialize" operation, behavior "A" will be changed to a sequential execution of "B" and "C" by default. Another kind of operations, "flatten" are often performed during behavior scheduling to change the behavior hierarchy. Continuing with our example, if behavior "B" itself is composed of "D" and "E" in parallel, a "flatten" operation on "B" removes "B" from "A" while promoting its sub-behaviors, "D" and "E" one level up. As the result, behavior "A" becomes a "par" composition of "D", "E" and "C". Note that the hierarchy relation among behaviors is most conveniently represented as a tree, operations "serialize tree" and "flatten tree" are also provided by SCE to serialize or flatten behaviors of a subtree recursively.

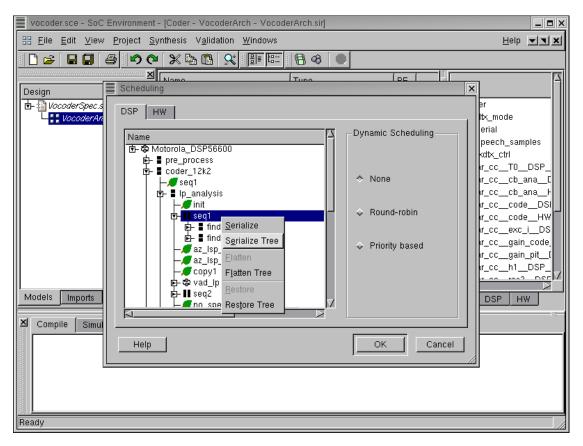

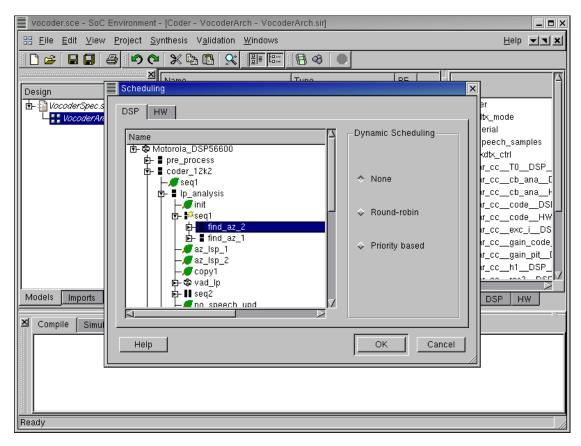

In our design, for example, to serialize the sub-behaviors of behavior "seq1", in the design hierarchy tree, select behavior "seq1". Right click to bring up a menu window and select Serialize Tree from the menu.

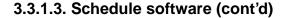

Now that the two parallel child behaviors of behavior "seq1": behavior "find\_az\_1" and behavior "find\_az\_2" are converted into two sequential behaviors. We can see that behavior "find\_az\_1" is executed before behavior "find\_az\_2". This execution order is created by the tool. The designer can modify the execution order.

Select behavior "find\_az\_2". Left click and move behavior "find\_az\_2" before behavior "find\_az\_1". Now behavior "find\_az\_2" is executed before "find\_az\_1". In general, the designer can specify any "par" or "pipe" statements to be scheduled and manually specify the execution order of any parallel behaviors in the same level. The remaining parallel behaviors can either be dynamically scheduled by the RTOS model or statically serialized by the tool.

Since we want the tool to schedule all the behaviors automatically, we restore the execution order created by the tool. Select behavior "find\_az\_1". Left click and move behavior "find\_az\_1" before behavior "find\_az\_2".

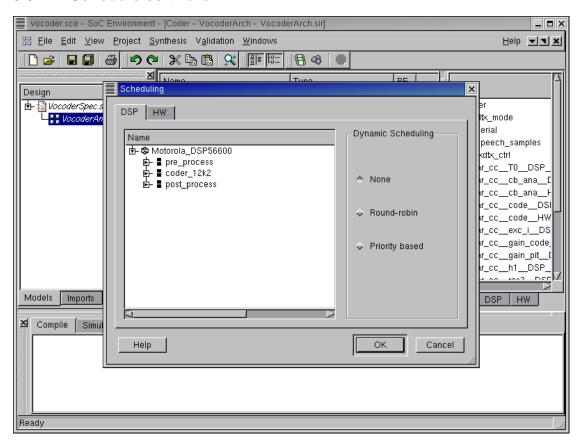

For our example, since there are not many parallel behaviors in DSP, we statically schedule the behaviors in DSP. In the dynamic scheduling box, click and select None.

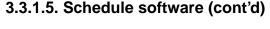

Also, we will leave the decision of behavior execution order to be made automatically by the tool. In the design hierarchy tree, select behavior "Motorola\_DSP56600". Right click and select Serialize Tree.

# 3.3.1.6. Schedule software (cont'd)

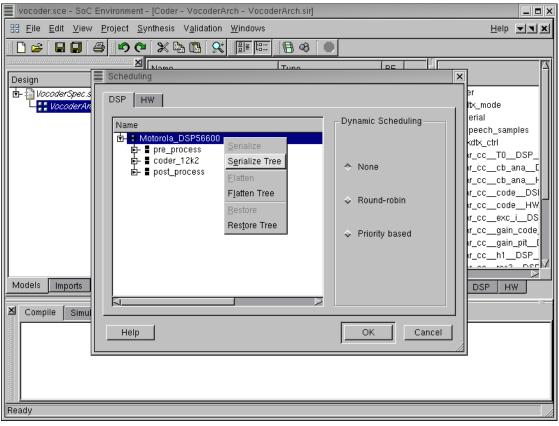

As shown in the figure, all the child behaviors of behavior "Motorola\_DSP56600" are serialized. Behaviors that are modified as a result of serialization are marked with a "\*" symbol next to them.

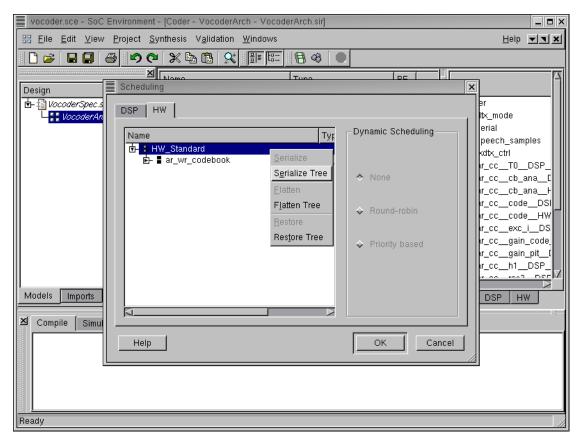

The next step is to serialize behaviors in HW. Since custom hardware can only be statically scheduled, the dynamic scheduling box is disabled for HW. Click and select HW in the Scheduling window. In the design hierarchy tree, select behavior "HW\_Standard". Right click and select Serialize Tree.

As shown in the figure, all the child behaviors of behavior "HW\_Standard" are serialized. Click OK button to confirm the scheduling decision.

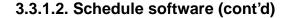

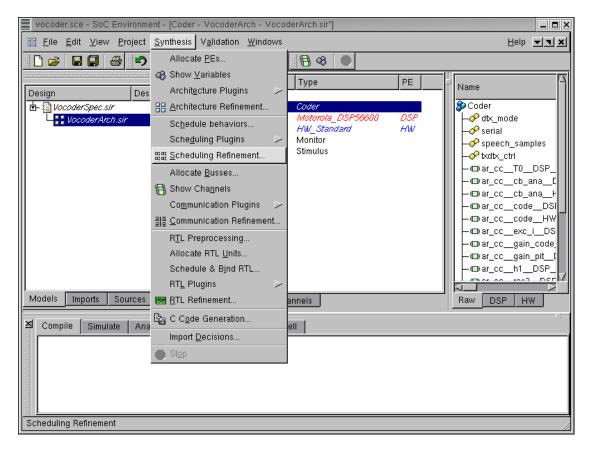

Once the scheduling decisions have been made, we can refine the architecture model to reflect the changes. A software scheduling and RTOS model insertion tool is integrated in SCE. The tool will generate the model to reflect the scheduling algorithm we selected. In case of dynamic scheduling, a RTOS model is inserted into the design and behaviors are converted into tasks with assigned priorities. To invoke the tool, go to Synthesis menu and select Scheduling Refinement.

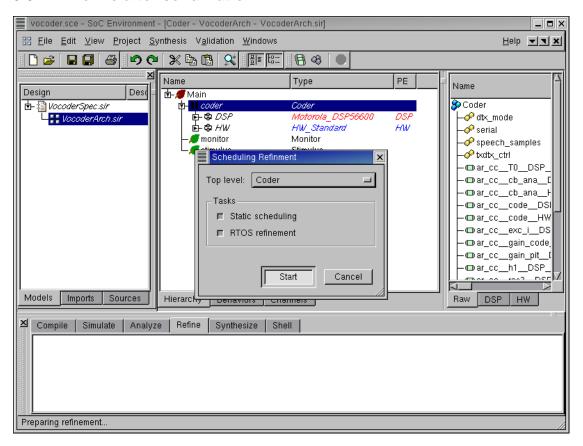

#### 3.3.2.1. Refine after serialization

A dialog box pops up for selecting specific refinement tasks. By default, all tasks will be performed in one go. Press the Start button to start the refinement.

It must be noted that the user has an option to do the refinement tasks one step at a time. For instance, a designer may select only static scheduling if he or she is not concerned about observing the dynamic scheduling behavior on the component.

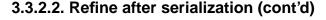

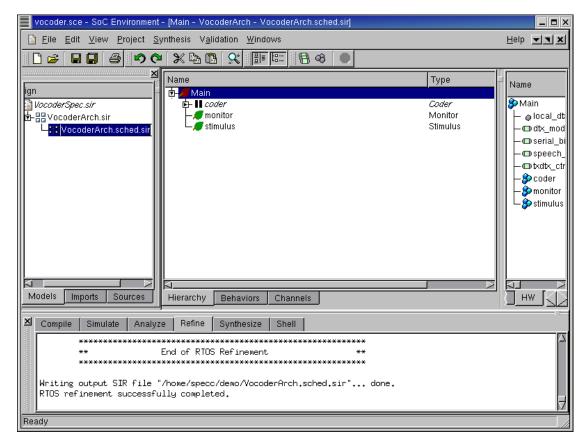

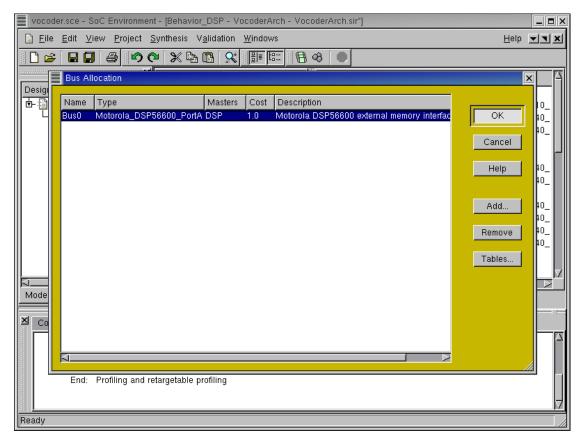

The logging window shows the refinement process. After the refinement, the newly generated serialized model "VocoderArch.sched.sir" is displayed to the design window. It is also added to the current project window, under the architecture model "VocoderArch.sir" to indicate that it was derived from "VocoderArch.sir".

## 3.3.2.3. Refine after serialization (cont'd)

As we did for previous models, we change the name of the serialized architecture model to "VocoderSched.sir" in the project window.

## 3.3.3. Simulate serialized model (optional)

This section shows the simulation of the generated model. If the reader is not interested, she or he can skip this section and go directly to Section 3.4 *Communication Synthesis* (page 112).

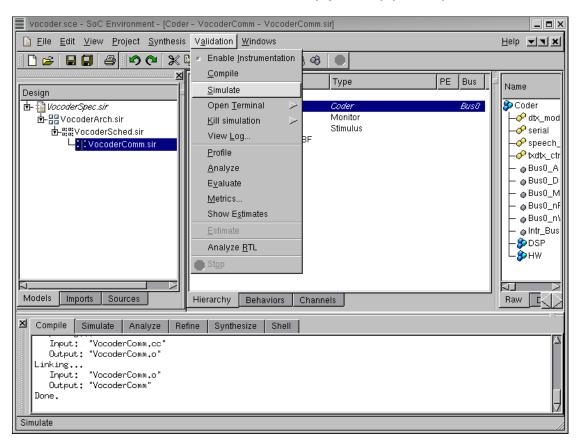

Serialization refinement is now complete with the generation of a new model. However, we also need to confirm that the model has not lost any of its functionality in the refinement process. In other words the new model must be functionally equivalent to the architecture model.

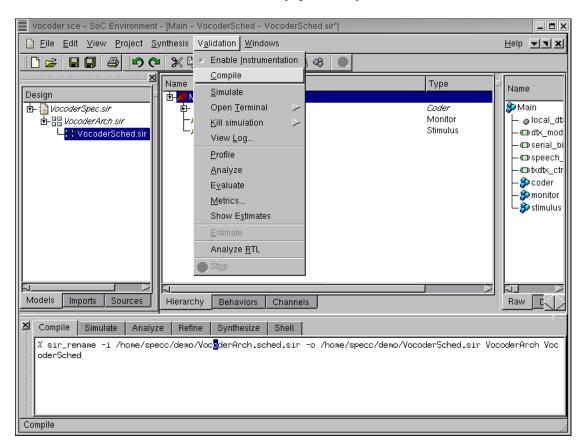

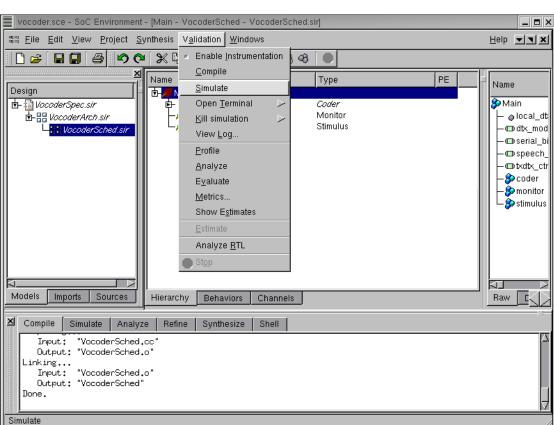

We will validate the serialized architecture model through simulation. But first we need to compile the model into an executable. To compile the serialized architecture model to executable, go to Validation menu and select Compile.

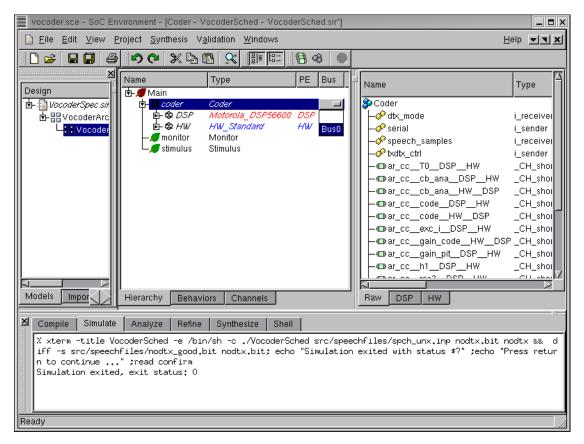

## 3.3.3.1. Simulate serialized model (optional) (cont'd)

The messages in the logging window shows that the refined model is compiled successfully without any errors. Now in order to verify that it is functionally equivalent to the architecture model, we will simulate the compiled model on the same set of speech data used in the specification validation. Go to Validation menu and select Simulate.

#### 3.3.3.2. Simulate serialized model (optional) (cont'd)

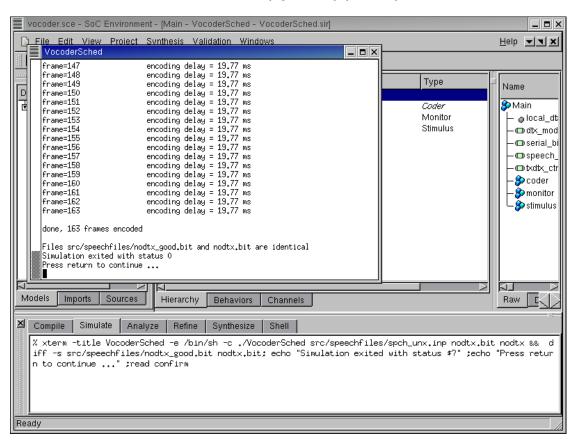

The simulation run is displayed in a new terminal window. As we can see, the serialized architecture model was simulated successfully for all 163 frames of speech data. The result bit file is also compared with the expected golden output given with the Vocoder standard. We have thus verified that the generated refined model is functionally correct. Note that the execution time for each frame now becomes 19.77 ms. Recall that the execution time was 16.35 ms for each frame before the software scheduling is performed. The increase of execution time is reasonable since the concurrency in the previous model is removed by the software scheduling.

# 3.4. Communication Synthesis

Communication synthesis is the second part of the system level synthesis process. It refines the abstract communication between components in the architecture model. Specifically, the communication with variable channels is refined into an actual implementation over wires of the system bus. The steps involved in this process are as follows.

We begin with allocation of system buses and selection of bus protocols. A set of system buses is selected out of the bus library and the connectivity of the components with system buses is defined. In other words, we determine a bus architecture for our design.

This is followed by grouping of abstract variable channels. The communication between system components has to be implemented with busses instead of variable channels. Thus these channels are grouped and assigned to the chosen system busses. Once this is done, the automatic refinement tool produces the required bus drivers for each component. It also divides variables into slices whose size is the same as width of the data bus. Therefore that each slice can be sent or received using the bus protocol. The entire variable is sent or received using multiple transfers of these slices.

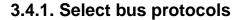

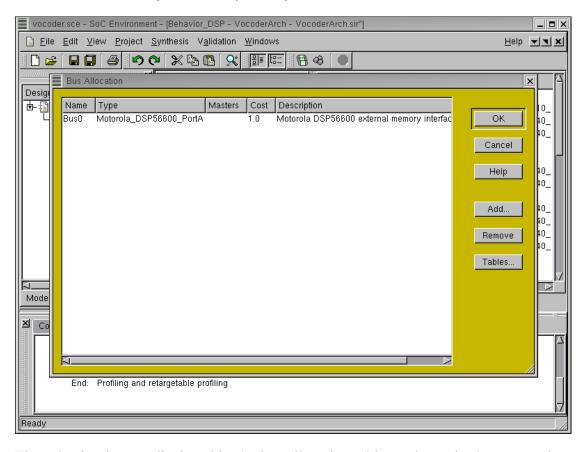

As explained earlier, we begin by selecting a suitable bus for our system. Note that in the presence of only two components, one bus would suffice. However, in general the user may select multiple buses if the need arises. Bus allocation is done by selecting Synthesis—Allocate Busses from the menu bar.

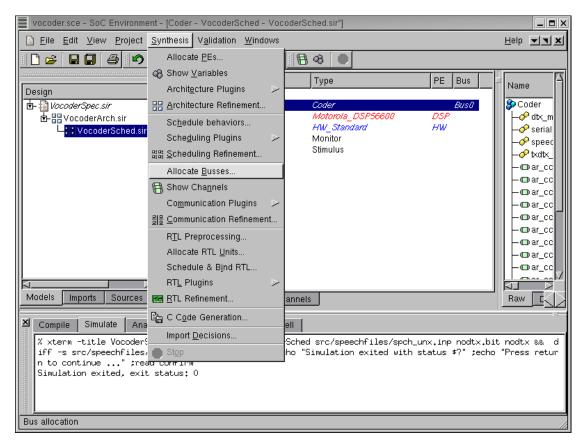

## 3.4.1.1. Select bus protocols (cont'd)

A Bus Allocation window pops up showing the bus allocation table. Since there are no busses selected at the time, this table is empty. We now click on Add to add bus(es) from the protocol database.

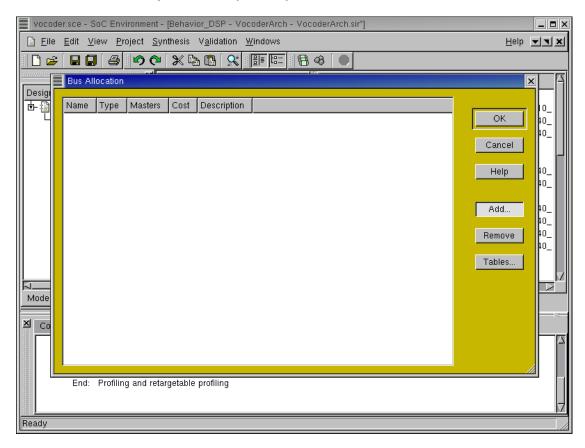

#### 3.4.1.2. Select bus protocols (cont'd)

A Bus Selection window pops up showing the contents of the protocol database. The column on the left shows the three categories of protocols. During component selection for architecture exploration, we had a classification of components. Likewise, the classification here shows us the available types of busses. On selecting a particular category with left click, the busses under that category are displayed. For our demo purposes, we select the Processor bus "Motorola\_DSP56600\_PortA" and click OK.

Note that the architecture chosen for the design has an impact on the selection of busses. More often that not, the primary component in the design dictates the bus selection process. In this case, we have a DSP with an associated bus. It makes sense for the designer to select that bus to avoid going through the overhead of generating a custom bus adapter.

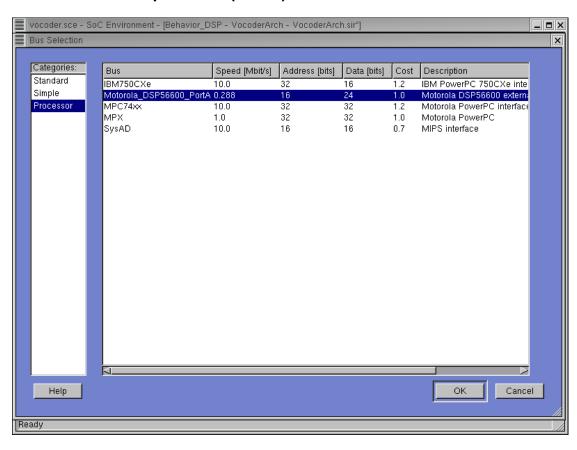

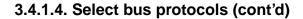

#### 3.4.1.3. Select bus protocols (cont'd)

The selection is now displayed in the bus allocation table as shown in the screen shot. A default name of "Bus0" is given to identify this system bus. In order to include this bus in the design, we need to specify which component is going to be the master on the bus. This is done by Left click under Masters column. Since this bus is for the Motorola 56600 processor that we have chosen, the master is the processor. Recall that the name given to the processor component was "DSP." We thus enter the name "DSP" under Masters column and press RETURN.

The bus selection is now complete and we can finish off with the allocation phase by left clicking on OK.

# 3.4.2. Map channels to buses

Once the bus allocation has been done, we need to group the channels of the architecture model and assign them to the system buses. Recall that in the architecture model, we had communication between components with abstract variable channels. We now have to assign those variable channels to the system bus.

Expand the design hierarchy window and scroll to the right to find a new column entry Bus.

Like component mapping, bus mapping may be done by assigning variable channels to buses. However, to speed things, we may assign the top level component to our system bus. Since we have only one system bus, all the channels will be mapped to it. This is done by left clicking in the row for the "Coder" behavior under the bus column. Select the default "Bus0" and press RETURN.

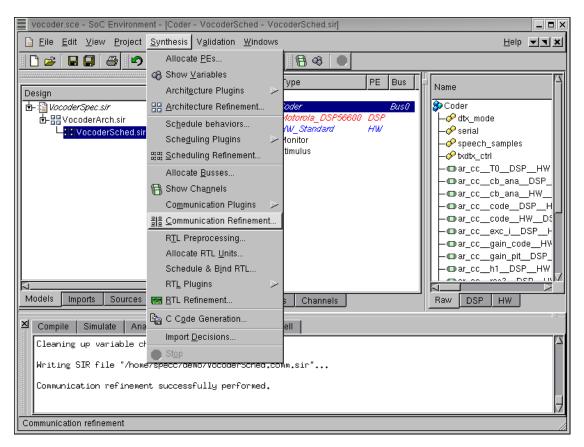

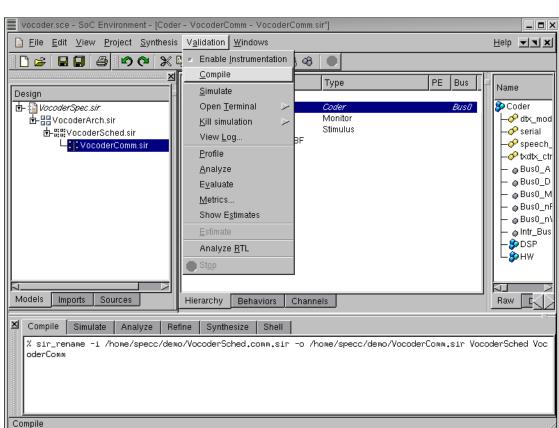

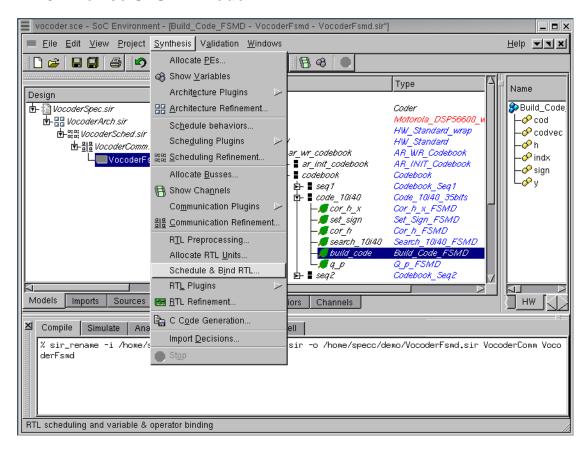

Now that we have completed bus allocation and mapping, we may proceed with communication refinement. Like architecture refinement, this process automatically generates a new model that reflects our desired bus architecture. To invoke the communication refinement tool, select Synthesis—>Communication Refinement from the menu bar.

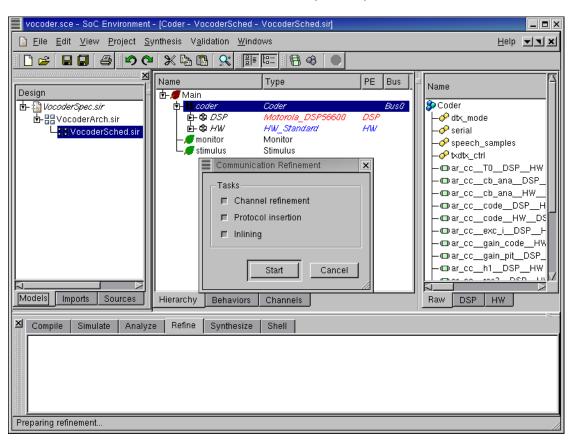

#### 3.4.3.1. Generate communication model (cont'd)

A new window pops up giving the user the option to perform various stages of the refinement. The user may choose to partially refine the model without actually inserting the bus, and only selecting the channel refinement phase. This way, he can play around with different channel partitions. Likewise, the user might want to play around with different bus protocols while avoiding "Inlining" them into components. This way he can plug and play with different protocols before generating the final inlined model. By default all the stages are performed to produce the final communication refinement. Since we have only one bus, and hence a default mapping, we opt for all three stages and left click on Start to proceed.

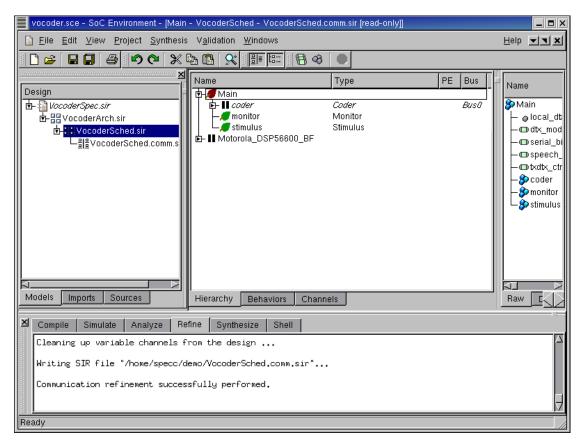

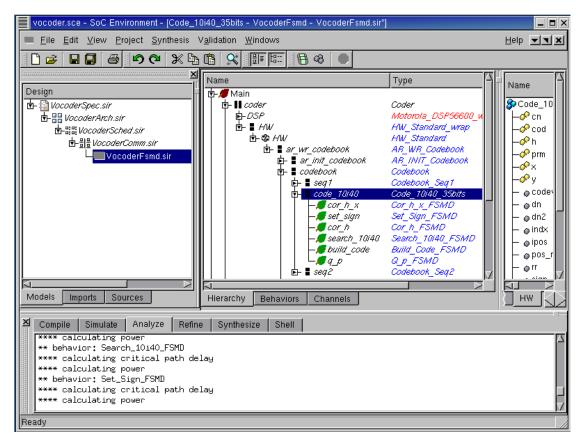

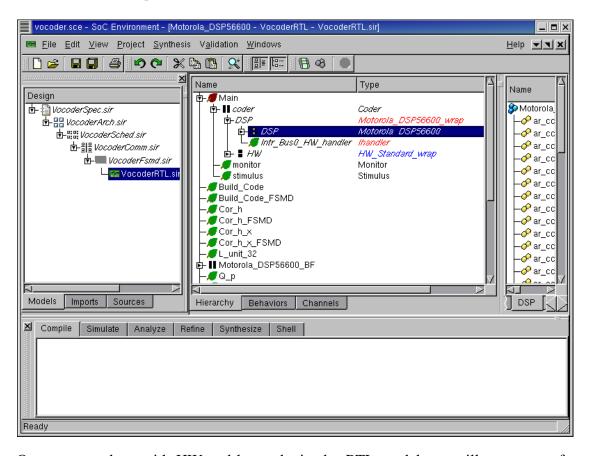

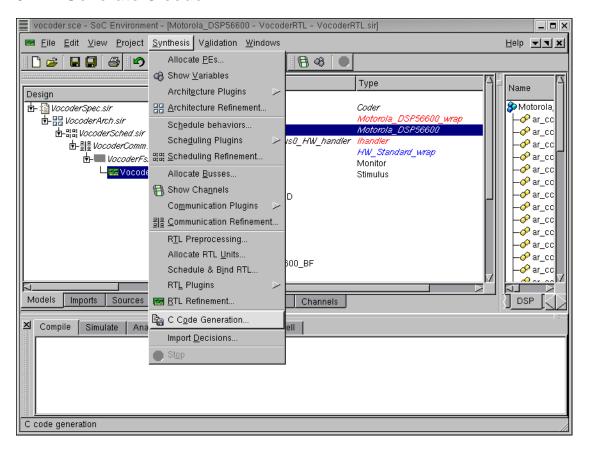

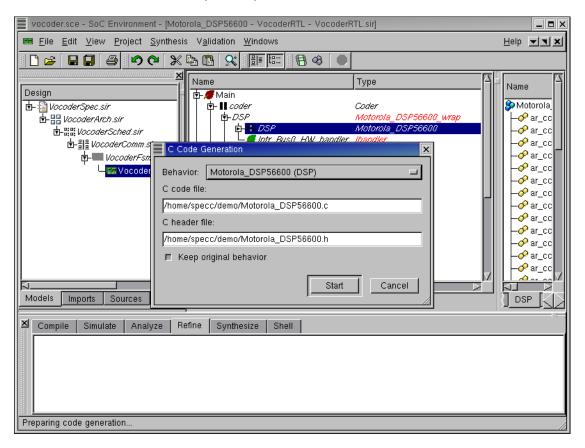

During communication refinement, note the various tasks being performed by the tool in the logging window. The tool reads in channel partitions, groups them together, imports selected busses and their protocols, implements variable channel communication on busses and finally inlines the bus drivers into respective components. Once communication refinement has finished, a new model is added in the project manager window. It is named "VocoderArch.comm.sir". Also note that we have a new design management window on the right side in the GUI.

### 3.4.3.3. Generate communication model (cont'd)

Ready

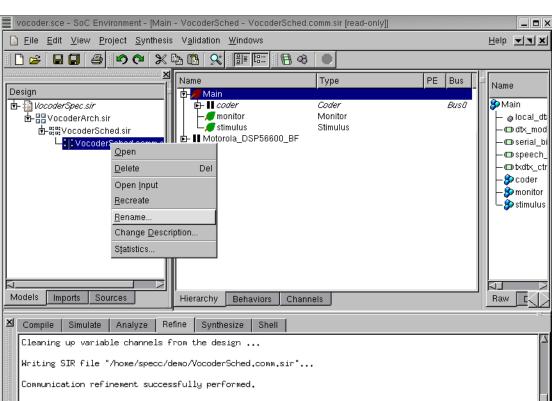

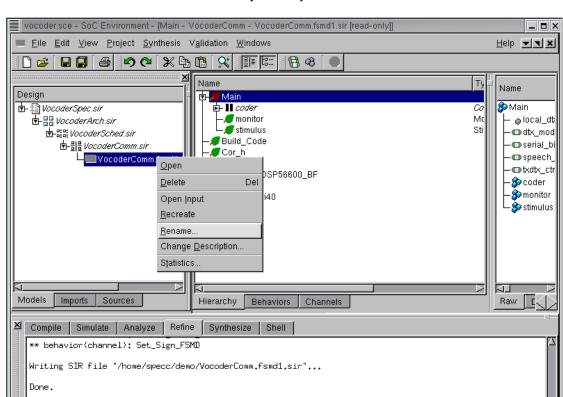

We now need to give our newly created communication model a reasonable name. To do this, right click on "VocoderArch.comm.sir" in the project manager window and select Rename from the pop-up menu. Now rename the model to "VocoderComm.sir".

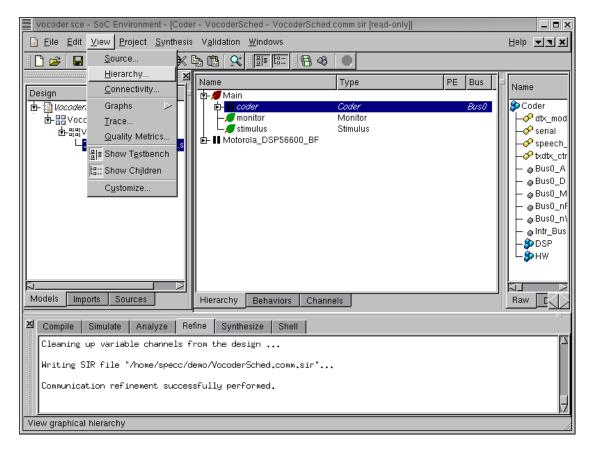

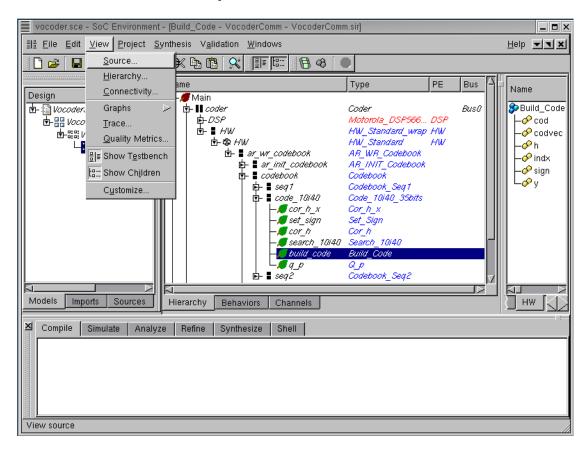

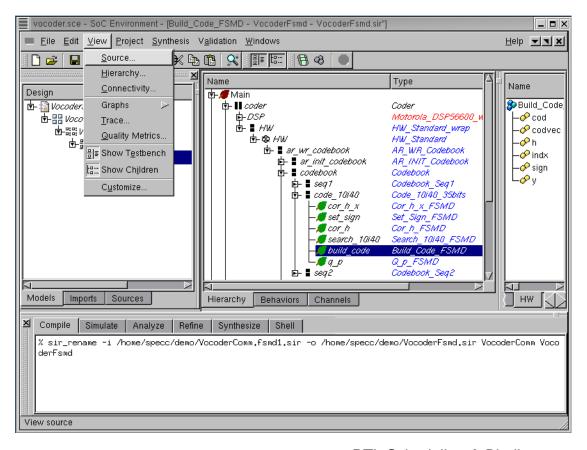

#### 3.4.4. Browse communication model

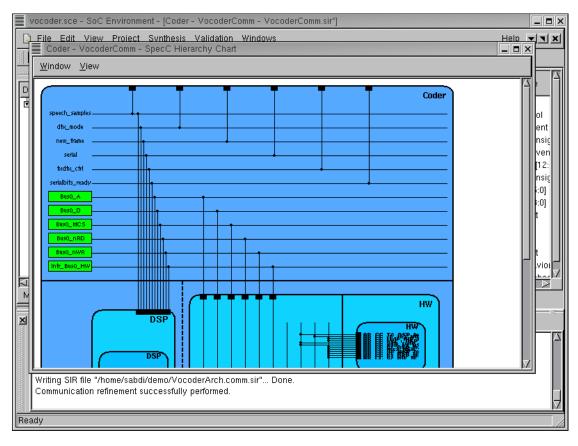

Like we did after architecture refinement, we browse through the communication model generated by the refinement tool. We have to first check whether it is semantically and structurally representing a model as described in our SoC methodology. To observe the model transformations produced by communication refinement, we need a graphical view of the model. This is done by left clicking to choose the "Coder" behavior in the design hierarchy window and selecting View—>Hierarchy from the menu bar.

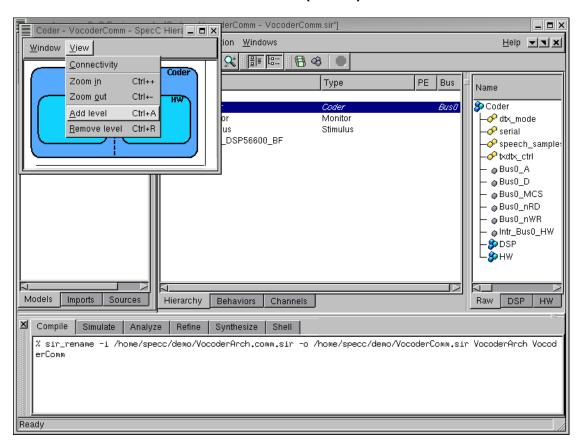

# 3.4.4.1. Browse communication model (cont'd)

A new window pops up showing the model with DSP and HW components. We have to observe the bus controllers generated during refinement and the added details to the model. Hence, we select View—Add level from the menu bar to view the model with greater detail.

## 3.4.4.2. Browse communication model (cont'd)

Writing SIR file "/home/sabdi/demo/VocoderArch.comm.sir"... Done.

Communication refinement successfully performed.

In the next level of detail, we can now see the interrupt handler "s0\_HW\_handler" behavior added in the master to serve interrupts from the HW slave. To view the actual wire connections of the system bus, enlarge window and select View—>Connectivity from the menu bar.

Ready

#### 3.4.4.3. Browse communication model (cont'd)

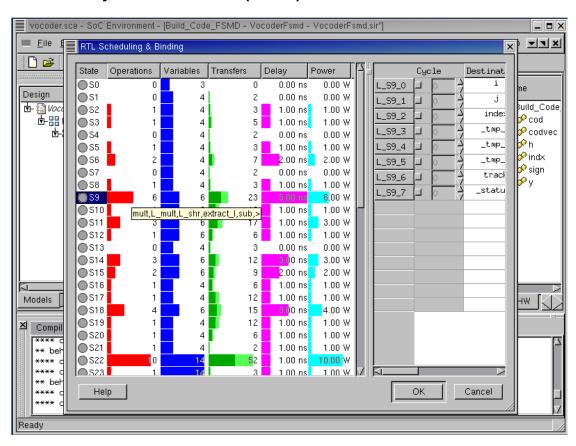

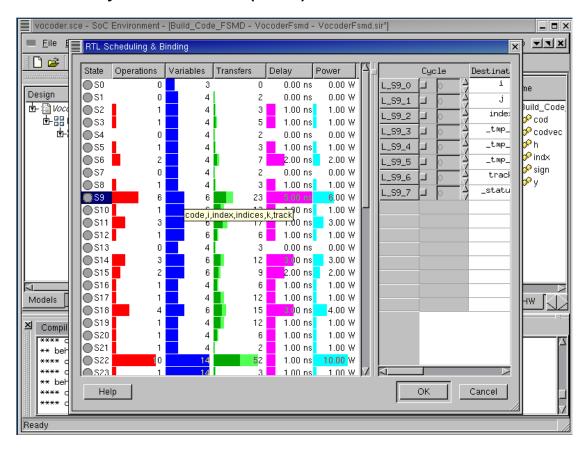

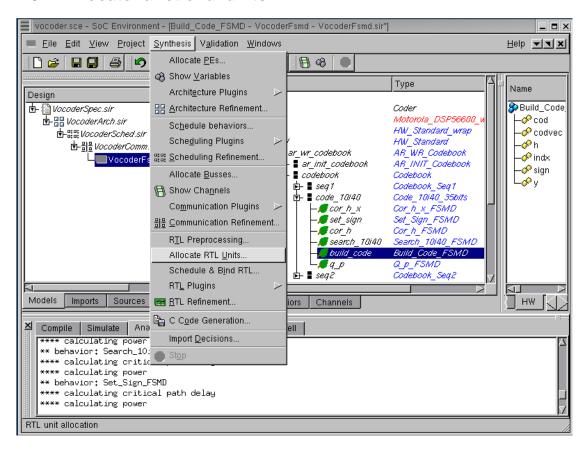

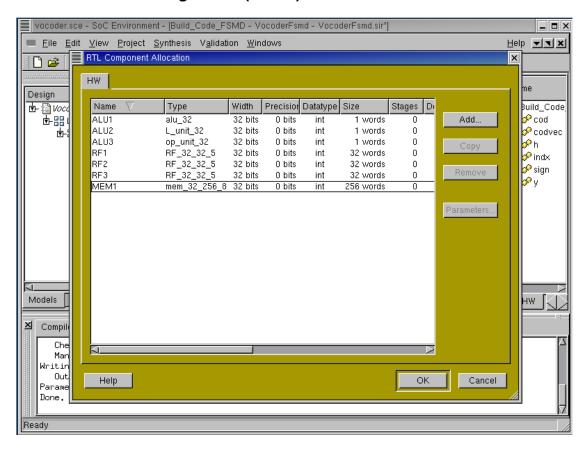

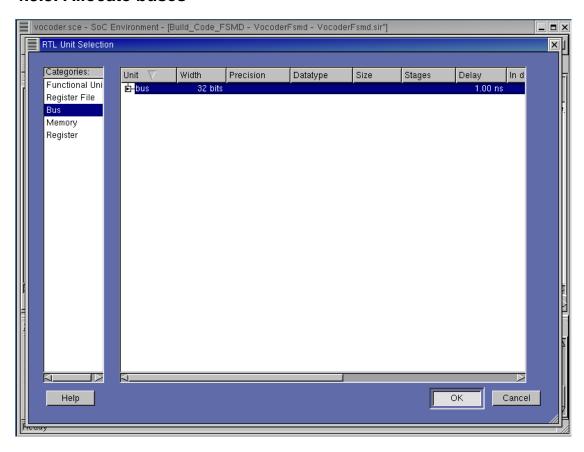

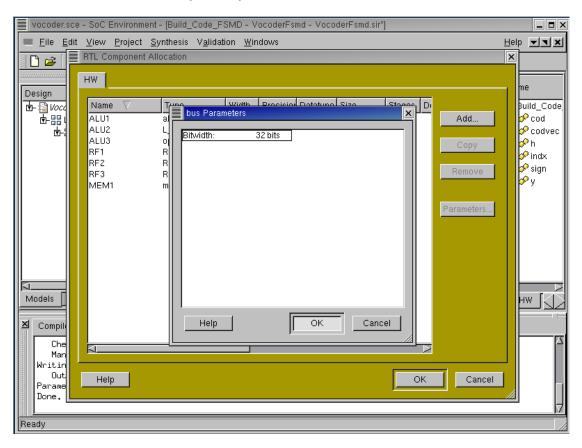

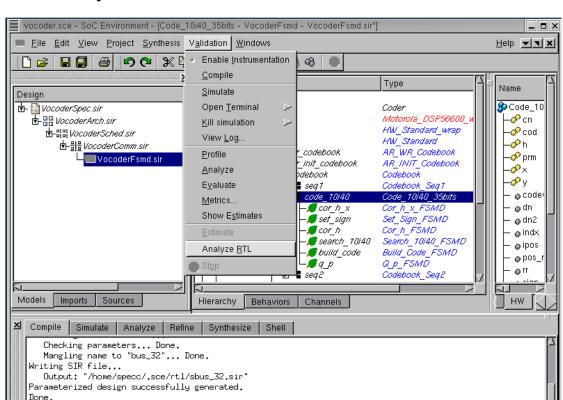

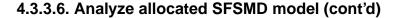

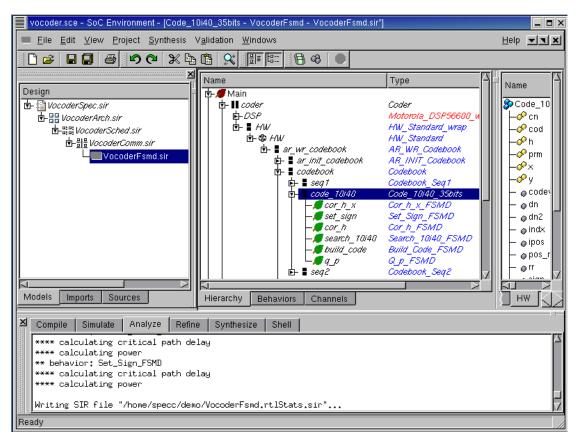

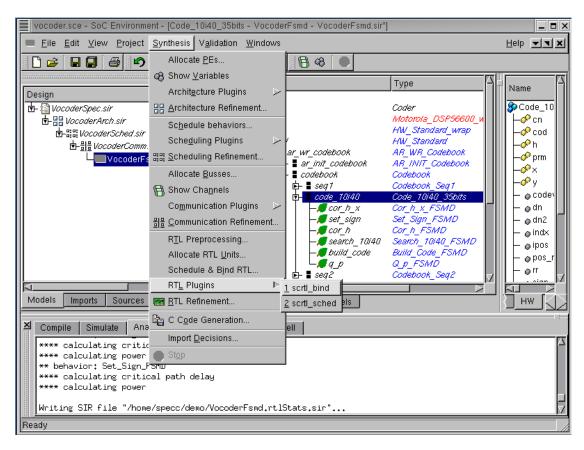

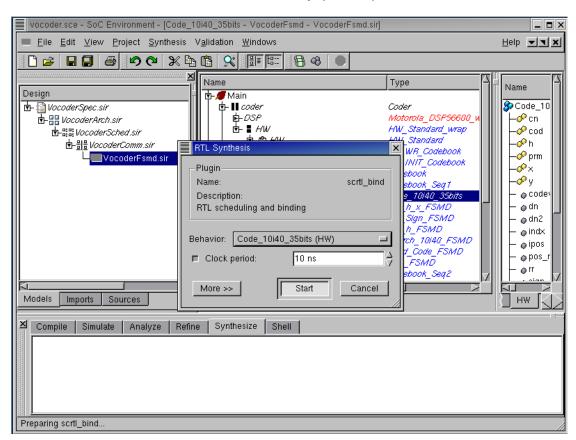

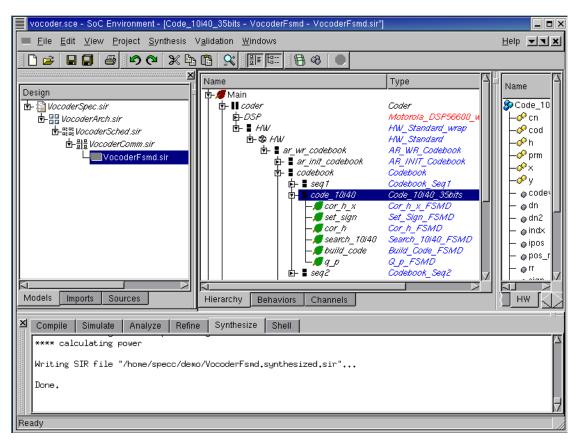

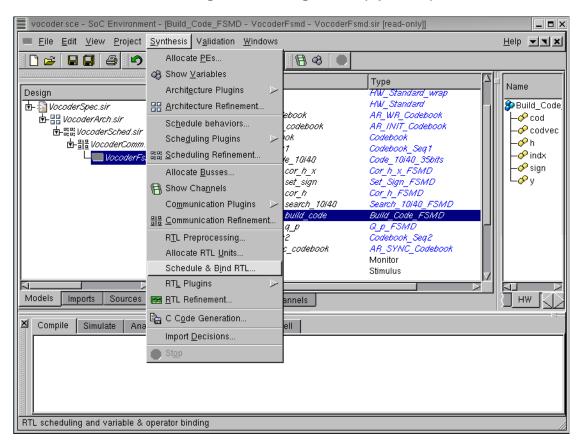

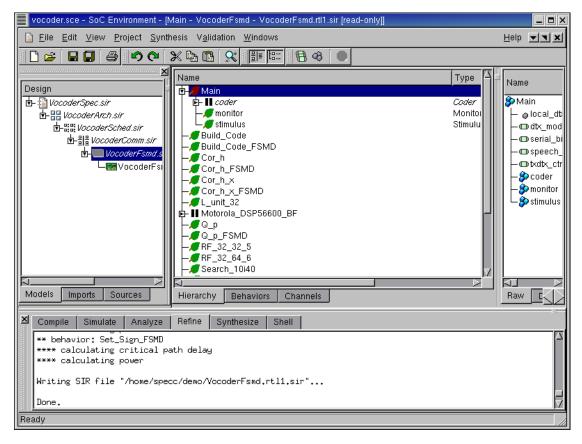

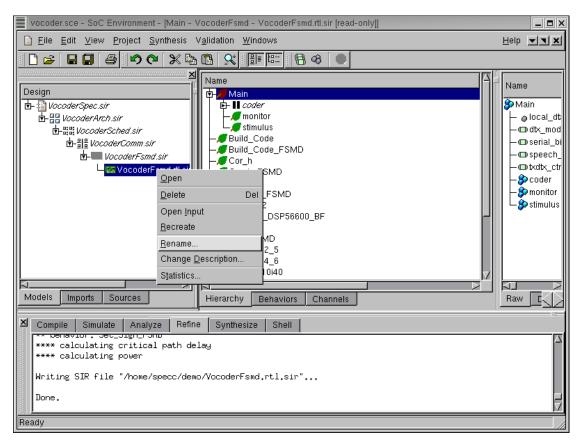

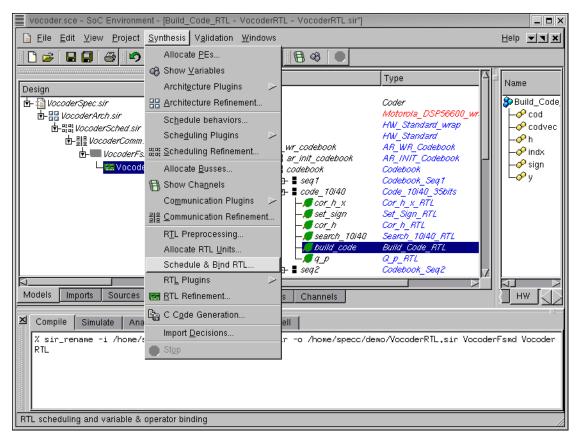

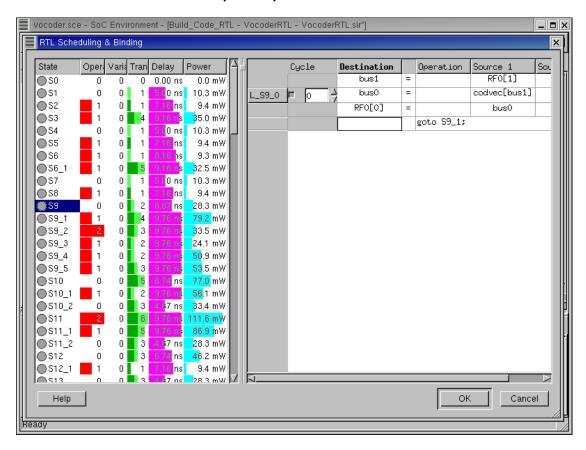

The wire level detail of the connection between components can now be seen in the window. Note that the system bus wires are distinguished by green boxes. Hence we see that the bus is introduced in the design and the individual components are connected with the bus instead of the abstract variable channels. On observing the hierarchical view further, we can see the drivers in each components. These drivers take the original variables and implement the high-level send/receive methods using the bus protocol.